# Design Of True Random Number Generation Using Pulsed Clock Generator

<sup>1</sup>Arava Haritha, <sup>2</sup>Sunil Kumar Jammala, <sup>3</sup>M. Swarna Lakshmi <sup>1</sup>PG Student, <sup>2</sup>Associate Professor, <sup>3</sup>Assistant Professor, Dept of ECE, <sup>1,2</sup>Narayana Engineering College, Nellore <sup>3</sup>Sri Venkateswara College of Engineering, Tirupati.

Abstract— True random number generators (TRNGs) expect an indispensable part in current cryptographic systems. Field programmable gate arrays (FPGAs) shape an ideal stage for gear executions of a critical number of these security calculations. In this short, we display an incredibly capable and tunable TRNG in perspective of the run of beat recurrence recognizable proof, especially for Xilinx-FPGA-based applications. The essential purposes of enthusiasm of the proposed TRNG are its on-the-fly tunability through one of a kind midway reconfiguration to improve randomness attributes. We portray the numerical model of the TRNG errands and exploratory results for the circuit completed on a Xilinx Virtex-V FPGA. The proposed TRNG has low hardware impression and intrinsic inclination end limits. The random piece streams made from it easily finish all tests in the NIST measurable suite.Index Terms—Digital clock manager test (DCM), dynamic partial reconfiguration (DPR), fieldprogrammable gate arrays (FPGAs), true random number generator (TRNG).

## **I.INTRODUCTION**

TRUE random number generators (TRNGs) have transformed into a basic part in various cryptographic systems, including PIN/watchword age, approval traditions, key age, random cushioning, and nonce age. TRNG circuits utilize a nondeterministic random process, typically as electrical noise, as a basic wellspring of randomness. Close by the fuss source, a tumult gathering instrument to isolate the confusion and a post planning stage to give a uniform measurable movement are other basic parts of the TRNG. Our focus is to design improved field-programmable gate show (FPGA) based TRNGs, using completely propelled parts. Using automated creating impedes for TRNGs has the good position that the diagrams are tolerably direct and suitable to the FPGA arrangement stream, as they can sensibly utilize the CAD programming instruments available for FPGA design.

Regardless, propelled circuits indicate moderately set number of wellsprings of random noise, e.g., meta steadfastness of circuit parts, recurrence of freerunning oscillators, and nerves (random stage shifts) in clock signals. As would be self-evident, our proposed TRNG circuit utilizes the recurrence difference of two oscillators and oscillator jitter as wellsprings of randomness.

The target of this brief is the blueprint, examination, and utilization of an easy to-design, improved, lowoverhead, and tunable TRNG for the FPGA organize. The going with are our genuine duties.

1) We investigate the limitations of the beat recurrence recognizable proof (BFD)- TRNG [3] when completed on a FPGA layout organize. To clarify the shortcomings, we propose an improved BFD-TRNG outline sensible for FPGA based applications. To the best of our understanding, this is the key reported work which merges tunability in a totally mechanized TRNG.

2) We analyze the balanced proposed plan numerically and likely.

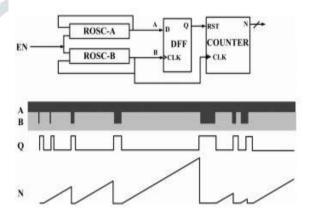

Fig. 1. Architecture of the single-phase BFD-TRNG [3].

3) Our preliminary comes to fruition solidly support the numerical model proposed. The proposed TRNG has low hardware overhead, and the random piece streams got from the proposed TRNG easily get through all tests in the NIST measurable test suite [4].

### **II.EXISTING SYSTEMS**

This section briefly describes the basic BFD-TRNG model and the DPR methodology utilizing DRP ports available in Xilinx CMTs.

### A. Single-Phase BFD-TRNG Model

The BFD-TRNG circuit [3] is a totally progressed TRNG, which relies upon jitter extraction by the BFD instrument, at first completed as a 65-nm CMOS ASIC. The structure and working of the (single stage) BFD-TRNG can be sketched out as takes after, in conjunction with Fig. 1.

1) The circuit contains two semi indistinct ring oscillators (let us term them as ROSCA and ROSCB), with relative advancement and position. As a result of characteristic physical randomness beginning from process assortment impacts related with significant sub micrometer CMOS creating, one of the oscillators (e.g., ROSCA) falters barely speedier than the other oscillator (ROSCB). Likewise, the makers [3] proposed to use trimming capacitors to furthermore tune the oscillator yield frequencies.

2) The yield of one of the ROs is used to test the yield of the other, using a D flip-droop (DFF). Without loss of comprehensive articulation, expect that the yield of ROSCA is maintained to the D-commitment of the DFF, while the yield of ROSCB is related with the clock commitment of the DFF.

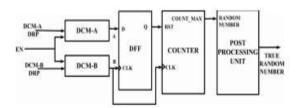

## Fig. 2. Overall architecture of the proposed DCMbased tunable BFD-TRNG.

4) A counter controlled by the DFF increases amid the beat frequency interims and gets reset because of the rationale 1 yield of the DFF. Because of the random jitter, the free running counter yield increase to various pinnacle esteems in every one of the check up interims before getting reset.

5) The yield of the counter is tested by an examining clock before it achieves its most extreme esteem.

## **B.Disadvantages of the BFD-TRNG**

One shortcoming of the past BFD-TRNG circuit is that its measurable randomness is liable to the arrangement idea of the ring oscillators. Any arrangement inclination in the ring oscillators may inimically impact the factual randomness of the bitstream made by the TRNG. Frameworks with a comparative number of inverters anyway uncommon circumstances achieved fluctuating counter maximas. Likewise, a comparative ring-oscillator-develop **BFD-TRNG** realized in light of different FPGAs of a comparative family shows indisputable counter maxima. Tragically, since the ring oscillators are free-running, it is difficult to control them to take out any arrangement tendency. The issue is exacerbated in FPGAs, where it is consistently difficult to control setup tendency because of the nonattendance of fine-grained originator control on directing in the FPGA diagram texture.

## III.PROPOSED SYSTEM (TUNABLE BFD-TRNG FOR FPGA-BASED APPLICATIONS )

### A.Design Overview

Fig. 2 shows the general designing of the proposed TRNG. Set up of two ring oscillators, two DCM modules make the influencing waveforms. The DCM locals are parameterized to make to some degree extraordinary frequencies by modifying two arrangement parameters M (duplication factor) and D (division factor). In the proposed diagram, the wellspring of randomness is the jitter showed in the DCM equipment. The DCM modules allow more imperative originator control over the clock waveforms, and their

Fig. 3. Architecture of tuning circuitry.

utilize takes out the necessity for basic arrangement [3]. Tunability is developed by setting the DCM parameters on-the-fly using DPR limits using DRP ports. This capacity gives the arrangement more imperative versatility than the ring-oscillator-based BFDTRNG

Besides, we have a direct post taking care of unit using a Von Neumann corrector (VNC) [5] to wipe out any biasing in the made random bits. VNC is an extraordinary low overhead intend to execute tendency from a random piece stream. In this arrangement, any data bit "00" or "11" plan is shed; something unique, if the data bit configuration is "01" or "10," simply the essential piece is held. The last three LSBs of the made random number are experienced the VNC. The VNC upgrades the measurable attributes at the cost of slight decreasing in throughput.

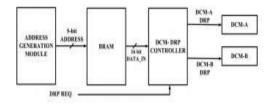

### **B.Tuning Circuitry**

The outline of the tuning equipment is showed up in Fig. 3. The target clock recurrence is directed by the course of action of parameter regards truly picked. The random regards came to by the counter and what's more the jitter are related to the picked parameters M and D (purposes of intrigue are analyzed in Section IV). This makes it possible to tune the proposed TRNG using the destined set away M and D regards. As unhindered DPR has been seemed, by all accounts, to be a potential threat to the circuit [6], the safe operational regard mixes of the D and M parameters for each DCM are predestined in the midst of the framework time and set away on an on-chip square RAM (BRAM) memory block in the FPGA.

## IV. MATHEMATICAL MODEL OF THE PROPOSED TRNG

### A.Circuit Behavior With PLL as Clock Generator

We initially consider the operational rule for the PLL and its attainability as a part of the proposed TRNG. The Xilinx PLL incorporates a clock flag whose recurrence is given by

$$F_{\rm CLKFX} = F_{\rm CLKIN} \cdot \frac{M}{D} \qquad \dots (1)$$

where FCLKIN is the recurrence of the data clock banner and M and D are the expansion and division factors as of now said. The estimations of M and D can be varied to make the required clock recurrence. The two PLLs can be parameterized with the fundamental game plan of (M,D) characteristics to make two insignificantly one of a kind clock loss of frequencies. Without comprehensive proclamation, expect that PLLA is set up to be to some degree speedier than PLLB, i.e., the periods are associated by TA < TB. On accomplishing the beat recurrence interval (e.g., n clock cycles), by definition, PLLA completes one cycle more than the slower one. The going with condition depicts this essential model:

$$\frac{T_A}{T_B} = \frac{N}{N+1}.$$

(2)

$N = 2 \cdot n$ , where n is the estimated maximum counter value. For the first n clock cycles, the counter does not increment and then increments by one for each of the next n clock cycles. Hence, the maximum counter values reached are n. Then, (2) leads to

$$n = \left\lfloor \frac{T_B}{2(T_B - T_A)} \right\rfloor.$$

...(3)

Using diagram course of action parameters (M and D), one of the oscillators is made to run speedier than the other. This is finished remembering the true objective to limit the extent of counter regards conveyed. This certifies the Xilinx PLL illustrations display closetoideal lead and are semi vague, and have immaterial jitter between the waveforms made by them. Since the BFDTRNG is essentially dependent on the closeness of jitter between the two made clock waveforms, PLLs have all the earmarks of being forbidden as sections of the proposed TRNG. Therefore, next we dissect the DCM as clock generators.

#### **B.Circuit Behavior With DCM as Clock Generator**

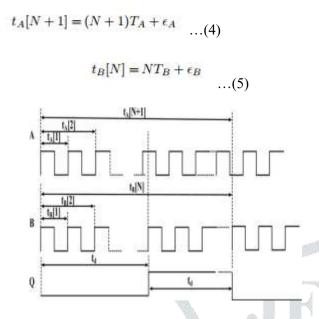

Without loss of comprehensive proclamation, the clock signals conveyed by one of the DCM (e.g., DCMA) are imperceptibly speedier than the other (DCMB), recommending TA < TB. This is ensured by selecting the arrangement parameters M and D as in (7). More purposes of intrigue are analyzed in Section IV-C. Timing blueprints of the DCM clock yields and the resultant DFF response are showed up in Fig. 4. Allow N to be the number of clock cycles of the

slower check movement in which the speedier clock signal completes exactly one cycle more. By then

# Fig. 4. Timing diagram of DCM output waveforms and the corresponding and DFF response.

where An and B are the vulnerabilities in light of jitter and DCMB, independently. in DCMA The vulnerabilities in view of jitter in DCMA and DCMB are unprecedented; this is by virtue of the DCMs are delineated with indisputable exhibiting parameters M and D. The relating jitter for every one of the DCMs used as a piece of the proposed arrangement is shown in Table III. Expecting that there is no metastability for the DFF if signal advances occur in the setup-hold timing window around its driving clock edge (the metastability issue can be avoided by fell DFF mix), the change time (td) of the DFF, the time interval after which it sets (i.e., the counter dictated by the DFF resets), is evaluated by

$$t_d = \frac{t_A[N+1] + t_B[N]}{2} = \frac{(N+1)T_A + NT_B + \epsilon_A + \epsilon_B}{2},$$

(6)

From (6), the advance time of DFF is a random system. The yield of the DFF, i.e., the time between time (td) after which the counter resets, is henceforth a random limit. In like manner, the check regard procured when the counter resets is also a random sum. The counter resets thusly when the DFF sets, and the undertaking continues. The DFF resets around n cycles after it sets, and the counter starts checking again.

#### **C. Tuning Parameter Value Ranges**

Equations (1) and (2) also hold true for DCM-based BFD. Hence, we have the following relationships:

$$\frac{D_1 \cdot M_2}{D_2 \cdot M_1} = \frac{N}{N+1} \begin{cases} 2 \le M_i \le 33, \\ 1 \le D_i \le 32, \\ 400 \le N \le 1000, \\ M_i, D_i, N \in \mathbb{Z} \\ \dots (7) \end{cases}$$

where M and D esteems are according to the Xilinx DCM determination [1]. The tally an incentive to be examined was set to be in the vicinity of 200 and 500; thus, the estimations of N are according to (7). Higher estimation of consider isn't wanted it prompts higher power scattering. According to (7), there are 23 sets of (M,D) esteem mixes for the two DCMs, which fulfill the required check run. These qualities are put away in a BRAM, and for 23 particular sets, we

### **TABLE I**

## HARDWARE FOOTPRINT OF THE PROPOSED TRNG

### AND THE RING-OSCILLATOR-BASED TRNG

| Design                         | Modale Name | Sic | SiceReg | LUTS | BUFG | DCM_ADV | PLL_ADV |

|--------------------------------|-------------|-----|---------|------|------|---------|---------|

| DCM-based TRNG                 | Oscillators | 4   | 0       | 4    | 4    | 2       | 0       |

|                                | DFF         | 1   | 1       | 0    | 0    | Ð       | 0       |

|                                | Couster     | 9   | 15      | 15   | 30   | 0       | 0       |

|                                | Total       | 14  | 26      | 19   | 34   | 2       | 0       |

| Ring Oscillator<br>-based TRNG | Oscillatars | 23  | 0       | 90   | 0    | Ð       | 0       |

|                                | DeF         | 1   | 1       | 0    | Ð    | Ð       | 0       |

|                                | Couster     | 9   | h       | 15   | 30   | Û       | 0       |

|                                | Sampler     | 0   | 0       | 0    | 1    | 0       | 1       |

|                                | Total       | .33 | 26      | 15   | 31   | Ð       | 1       |

### **TABLE II**

### ON-CHIP POWER DISSIPATION OF THE PROPOSED TRNG

#### AND THE RING-OSCILLATOR-BASED TRNG

| On-Chip                        | Clock | Logic | Signal | BRAM  | PLL   | DCM   | 10    | Leakage | Total |

|--------------------------------|-------|-------|--------|-------|-------|-------|-------|---------|-------|

| DCM<br>-based TRNG             | 0.098 | 0,001 | 0.002  | 0.003 | 0.134 | 0.136 | 0.034 | 1.962   | 1.470 |

| King Oscillator<br>-based TRNG | 0.053 | 0.000 | 0.062  | 0.000 | 0.268 | 0.000 | 0.000 | 1.061   | 1.384 |

require 5-bit address line for picking one of the blends of M and D regards, and if the BRAM isconfigured to hold 16-bit words, we require 46 B of memory. To dodge malicious changes by methods for DPR, we have enabled DPR restrictively by securing the permissible exhibiting parameters. With a particular true objective to complete this ensured tunable arrangement, to some degree higher hardware overhead and power dispersing are required. The DCM-DRP controller begins DPR in DCMA and DCMB using standard Xilinx plot approach [1].

## V. EXPERIMENTAL RESULTS

The final output of DCM based True Random Number Generator

## VI. CONCLUSION

We have shown an upgraded completely computerized tunable TRNG for FPGA-based applications, in perspective of the rule of BFD and clock jitter, and with worked in botch cure capacities. The TRNG utilizes this tunability incorporate for choosing the level of randomness, subsequently giving an abnormal state of versatility for various applications. The proposed setup effectively completes all NIST measurable tests.

## REFERENCES

[1] Virtex-5 FPGA Configuration User Guide UG 191 (v3.11) Xilinx Inc., San Jose, CA,USA,Accessed:May2016.[Online].Availablewww. xilinx.com/support/documentation/user\_guides/ug191. pdf

[2] A. P. Johnson, R. S. Chakraborty, and D.

Mukhopadhyay, "A PUF-enabled secure architecture for FPGA-based IoT applications," IEEE Trans. MultiScale Comput. Syst., vol. 1, no. 2, pp. 110–122, Apr.–Jun. 1, 2015.

[3] Q. Tang, B. Kim, Y. Lao, K. K. Parhi, and C. H. Kim, "True random number generator circuits based

on single- and multi-phase beat frequency detection," in Proc. IEEE Custom Integr. Circuits Conf., Sep. 2014, pp. 1–4.

[4] A. Rukhin, J. Soto, J. Nechvatal, M. Smid, and E. Barker, "A statistical test suite for random and pseudorandom number generators for cryptographic applications," Nat. Inst. Standards Technol. (NIST), Gaithersburg, MD, USA, DTIC Document, Tech. Rep., 2001.

[5] J. Von Neumann, "Various techniques used in connection with random digits," Nat. Bureau Standards Appl. Math. Ser., vol. 12, pp. 36–38, 1951.

[6] A. P. Johnson, S. Saha, R. S. Chakraborty, D. Mukhopadyay, and S. Gören, "Fault attack on AES via hardware Trojan insertion by dynamic partial reconfiguration of FPGA over Ethernet," in Proc. 9th WESS, Oct. 2014, pp. 1–8.

[7] A. P. Johnson, R. S. Chakraborty, and D. Mukhopadhyay, "A novel attack on a FPGA based true random number generator," in Proc. 10th WESS, Oct. 2015, pp. 1–6.