# Design of a Low Complexity Fault Tolerant Parallel FFT Using The Parity-SOS-ECC Technique

# <sup>1</sup>A.Shankaraiah, <sup>2</sup>Dr.D.Nageshwar Rao,

<sup>1</sup> M.Tech Student <sup>2</sup> Professor and Head of the Department, <sup>1,2,</sup> ECE Department, <sup>1,2,</sup> TKR College of Engineering & Techno logy, Meerpet, Hyderabad.

Abstract : Delicate mistakes emerge because of CMOS scaling in a few electronic circuits. Delicate mistakes are no exemption to the correspondence and flag handling frameworks. These blunders can be recognized and redressed by some algorithmic-based adaptation to non-critical failure (ABFT) procedures. One of them is the Fast Fourier Transform (FFTs) is a key building hinder in many flag handling frameworks. Numerous strategies have been proposed to identify and amend blunders in FFTs. Among those one of them is the Parseval check or entirety of squares strategy which is generally known. A few pieces are working in parallel for some correspondence frameworks. As of late, a strategy that adventures to actualize adaptation to non-critical failure on parallel channels has been proposed. In this paper two insurance systems have been proposed in that parseval check is utilized to recognize numerous blame FFTs however revises just single mistake at once. The second method is the equality SOS-ECC blame tolerant parallel FFTs strategy is utilized to lessen the quantity of SOS checks required. The second strategy likewise used to identify and rectify single mistake at once because of this it has the drawback of time delay. The proposed system investigations the rationale estimate, zone, postponement and power utilization utilizing Xilinx 12.2.

Index Terms - Error Correction Codes (ECCs), Fast Fourier Transforms (FFTs), Soft Errors...

#### I. INTRODUCTION

The many-sided quality of correspondences and flag handling circuits expands each year. This is made conceivable by the CMOS innovation scaling that empowers the coordination of an ever increasing number of transistors on a solitary gadget. This expanded many-sided quality makes the circuits more helpless against mistakes. In the meantime, the scaling implies that transistors work with bring down voltages and are more vulnerable to mistakes caused by commotion and assembling varieties. The significance of radiation-instigated delicate mistakes additionally increments as innovation scales. Delicate blunders can change the intelligent estimation of a circuit hub making a brief mistake that can influence the framework operation. To guarantee that delicate mistakes don't influence the operation of a given circuit, a wide assortment of methods can be utilized. These incorporate the utilization of unique assembling forms for the coordinated circuits like, for instance, the silicon on encasing. Another choice is to plan essential circuit pieces or finish outline libraries to limit the likelihood of delicate mistakes. At long last, it is additionally conceivable to include excess at the framework level to distinguish and adjust blunders.

One traditional case is the utilization of triple measured repetition (TMR) that triples a square and votes among the three yields to recognize and redress mistakes. The fundamental issue with those delicate mistakes relief procedures is that they require an extensive overhead as far as circuit usage. For instance, for TMR, the overhead is >200%. This is on account of the unprotected module is reproduced three times (which requires a 200% overhead versus the unprotected module), and also, voters are expected to revise the mistakes making the overhead >200%. This overhead is unreasonable for some applications. Another approach is to endeavour to utilize the algorithmic properties of the circuit to identify/rectify mistakes. This is normally alluded to as calculation based adaptation to non-critical failure (ABFT). This system can diminish the overhead required to ensure a circuit.

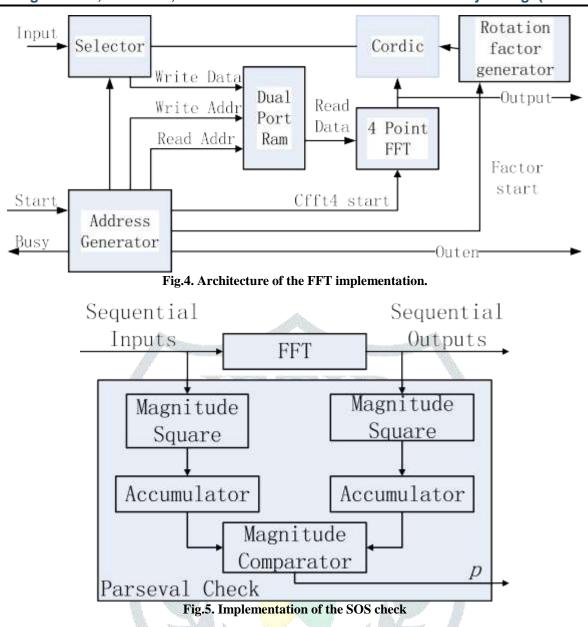

Flag handling and interchanges circuits are appropriate for ABFT as they have standard structures and numerous algorithmic properties. Throughout the years, numerous ABFT procedures have been proposed to ensure the fundamental obstructs that are usually utilized as a part of those circuits. A few works have considered the assurance of computerized channels. For instance, the utilization of replication utilizing decreased exactness duplicates of the channel has been proposed as another option to TMR however with a lower cost. The information of the dispersion of the channel yield has likewise been as of late misused to recognize and remedy mistakes with bring down overheads. The insurance of quick Fourier changes (FFTs) has additionally been broadly examined. As flag preparing circuits turn out to be more intricate, it is normal to discover a few channels or FFTs working in parallel. This happens for instance in channel banks or in numerous info various yield (MIMO) correspondence frameworks. Specifically, MIMO orthogonal recurrence division balance (MIMO-OFDM) frameworks utilize parallel IFFTs/FFTs for regulation/demodulation. MIMO-OFDM is actualized on long haul development portable frameworks and furthermore on Wi Max. The nearness of parallel channels or FFTs makes a chance to execute ABFT systems for the whole gathering of parallel modules rather than for every one freely. This has been contemplated for advanced channels at first in where two channels were considered. All the more as of late, a general plan in light of the utilization of blunder rectification codes (ECCs) has been proposed. In this procedure, the thought is that each channel can be what might as well be called a bit in an ECC and equality check bits can be figured utilizing expansion. This procedure can be utilized for operations, in which the yield of the whole of a few data sources is the entirety of the individual yields. This is valid for any direct operation as, the discrete Fourier change (DFT). In this short; the insurance of parallel FFTs is contemplated. Specifically, it is expected that there must be a solitary blunder on the framework at any given point in time. This is a typical presumption while considering the security against radiation-actuated delicate blunders. There are three primary commitments in this brief.

1) The assessment of the ECC system for the insurance of parallel FFTs demonstrating its adequacy as far as overhead and security viability.

2) The proposition of another system in view of the utilization of Parseval or entirety of squares (SOSs) checks joined with a parity FFT.

3) The proposition of another method on which the ECC is utilized on the SOS checks rather than on the FFTs.

The two proposed strategies give new contrasting options to secure parallel FFTs that can be more proficient than ensuring each of the FFTs freely.

The proposed plans have been assessed utilizing FPGA usage to evaluate the insurance overhead. The outcomes demonstrate that by consolidating the utilization of ECCs and Parseval checks, the security overhead can be lessened contrasted and the utilization of just ECCs as proposed in. Blame infusion tests have additionally been directed to confirm the capacity of the usage to identify and redress mistakes.

#### II. STUDY AND ANALYSIS OF PROTECTION SCHEMES FOR PARALLEL FFTS

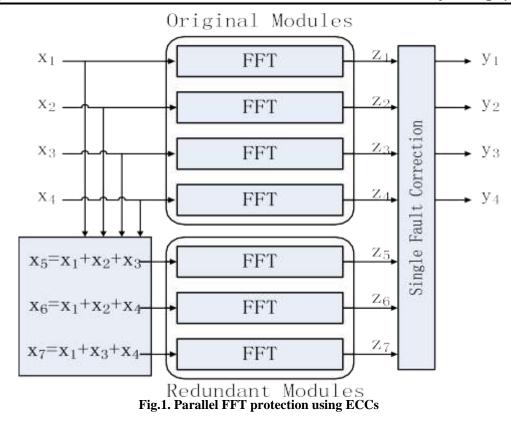

The beginning stage for our work is the assurance plot in light of the utilization of ECCs that was exhibited in for advanced channels. This plan is appeared in Fig.1. In this illustration, a basic single blunder rectification Hamming code is utilized. The first framework comprises of four FFT modules and three excess modules is added to distinguish and amend blunders. The contributions to the three excess modules are straight mixes of the sources of information and they are utilized to check direct blends of the yields. For instance, the contribution to the principal repetitive module is

$$X5 = x1 + x2 + x3 - - - (1)$$

What's more, since the DFT is a direct operation, its yield z5 can be utilized to watch that

$$z5 = z1 + z2 + z3 - - - (2)$$

This will be signified as c1 check. A similar thinking applies to the next two excess modules that will give checks c2 and c3. In light of the distinctions saw on each of the checks, the module on which the blunder has happened can be resolved. The diverse examples and the comparing mistakes are abridged in Table I. Once the mistake in module is known, at that point the blunder can be rectified by remaking its yield utilizing the rest of the modules. For instance, for a mistake influencing z1, this should be possible as takes after:

$$z_1c[n] = z_5[n] - z_2[n] - z_3[n] - (3)$$

Comparable amendment conditions can be utilized to remedy mistakes on alternate modules. Further developed ECCs can be utilized to revise mistakes in numerous modules if that is required in a given application. The overhead of this system, is lower than TMR as the quantity of excess FFTs is identified with the logarithm of the quantity of unique FFTs. For instance, to ensure four FFTs, three redundant FFTs are required, yet to secure eleven, the quantity of excess FFTs in just four. This shows how the overhead reductions with the quantity of FFTs.

| Table 1. Error Locatio | in in the framming Coue |

|------------------------|-------------------------|

| c1c2c3                 | Error bit position      |

| 000                    | No error                |

| 111                    | z1                      |

| 110                    | z2                      |

| 101                    | z3                      |

| 011                    | z4                      |

| 100                    | z5                      |

| 010                    | z6                      |

| 001                    | z7                      |

|                        |                         |

| Table 1 | l: Error | Location ir | 1 the H | lamming | Code |

|---------|----------|-------------|---------|---------|------|

|         |          |             |         |         |      |

Throughout the years, numerous systems have been proposed to secure the FFT. One of them is the Sum of Squares (SOSs) watch that can be utilized to distinguish blunders. The SOS check depends on the Parseval hypothesis that expresses that the SOSs of the contributions to the FFTs are equivalent to the SOSs of the yields of the FFTs aside from a scaling factor. This relationship can be utilized to identify blunders with low overhead as one increase is required for each information or yield test (two augmentations and adders for SOS per test).

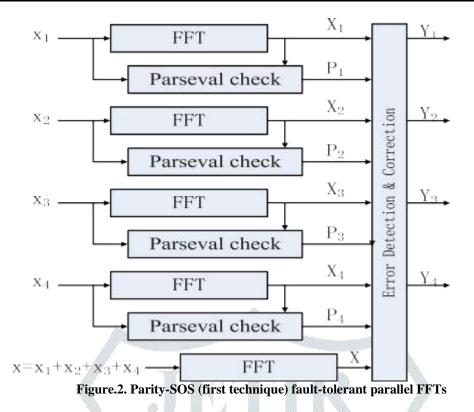

For parallel FFTs, the SOS check can be joined with the ECC approach. To lessen the security overhead for parallel FFTs, the SOS check can be joined with the ECC strategy. Since the SOS check recognizes just blunders and the ECC part ought to have the capacity to actualize the revision of mistakes. This should be possible by doling out basic equality bit for all the FFTs. Likewise, the SOS check is utilized on each FFT to identify blunders. At the point when a blunder is identified, the yield of the equality FFT can be utilized to amend the mistake. This is clarified with a case in Fig.2; the principal proposed procedure is outlined for the instance of four parallel FFTs. An excess (the equality) FFT is included that has the aggregate of the contributions to the first FFTs as information. A SOS check is likewise added to every unique FFT. In the event that a blunder is distinguished (utilizing P1, P2, P3, P4), the adjustment should be possible by recomputing the FFT in mistake utilizing the yield of the equality FFT (X) and whatever is left of the FFT yields. For instance, if a mistake happens in the primary FFT, P1 will be set and the blunder can be rectified by doing

$$X1c = X - X2 - X3 - X4 - (4)$$

This blend of a parity FFT and the SOS check diminishes the quantity of extra FFTs to only one and may, subsequently, decrease the assurance overhead; this will be alluded as equality

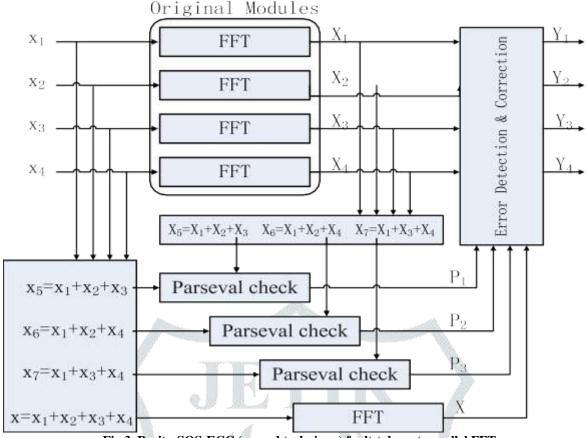

SOS procedure (or first proposed strategy). Another procedure is to consolidate the SOS check and the ECC approach is as opposed to utilizing a SOS check for every FFT, this will be alluded as equality SOS-ECC system (or second proposed strategy) is appeared in figure.3.

Fig.3. Parity-SOS-ECC (second technique) fault-tolerant parallel FFTs.

Table 2: Overhead Of The Different Schemes To Protect K- FFTS

| FFTs          | SOS checks    |

|---------------|---------------|

| $1 + \log(K)$ | 0             |

| 1             | K             |

| 1             | $1 + \log(K)$ |

|               |               |

In the equality SOS procedure, an extra equality FFT is utilized to adjust the blunders. The fundamental advantage over the principal equality SOS strategy is to diminish the quantity of SOS checks required. The blunder area procedure of equality SOS-ECC method is same with respect to the ECC strategy in Fig.1 and adjustment is as in the equality SOS system. The overheads of the two proposed procedures can be at first assessed utilizing the quantity of extra FFTs and SOS check pieces required. This data is abridged in Table II for an arrangement of k unique FFT modules expecting k is an energy of two. It can be watched that the two proposed systems lessens the quantity of extra FFTs to only one. Likewise, the second strategy additionally diminishes the quantity of SOS checks. A definite assessment for a FPGA usage is talked about to show the relative overheads of the proposed procedures. In every one of the methods, delicate blunders can likewise influence the components included for insurance. For the ECC system, the assurance of these components was examined. On account of the excess or equality FFTs, a blunder will have no impact as it won't engender to the information yields and won't trigger a remedy. On account of SOS checks, a blunder will trigger an adjustment when very is no mistake on the FFT. This will cause a superfluous remedy however will likewise deliver the right outcome. At long last, blunders on the location and rectification hinders in Figs.2 and 3 can spread mistakes to the yields. In our executions, those squares are secured with TMR. The same applies for the adders used to process the contributions to the repetitive FFTs in Fig.1 or to the SOS checks in Fig.3. The triplication of these squares small affects circuit intricacy as they are considerably less complex than the FFT calculations. A last perception is that the ECC strategy can identify all mistakes that surpass a given edge (given by the quantization used to actualize the FFTs). Then again, the SOS check distinguishes most mistakes yet does not ensure the recognition of all blunders. Along these lines, to think about the three procedures for a given usage, blame infusion tests ought to be done to decide the level of errors that are actually corrected. This means that an evaluation has to be done both in terms of overhead and error coverage.

#### Weaknesses:

• The ECC system is the excess technique, which is utilized to identify single mistake, and revises the single blunder blames as it were.

• The equality SOS strategy or first proposed procedure is the parseval check technique, it recognizes numerous blame FFTs yet revises just single blame at once.

• The equality SOS-ECC method or second proposed procedure is the mix of blunder remedy code and parseval check. This strategy likewise has the weakness of remedying single mistake.

• At a period single blunder can be distinguished and adjusted on account of this issue equality SOS-ECC procedure has the inconvenience of time delay.

## **Points Of Interest:**

- The two proposed procedures lessens the quantity of extra FFTs to only one.

- The principle advantage over the main equality SOS method is to diminish the quantity of SOS checks required.

- The equality SOS-ECC system lessens the usage multifaceted nature.

- The equality SOS-ECC system enhances the mistake location ability.

- The equality SOS-ECC system lessens the deferral, region and power contrasted with equality SOS strategy.

# **III.** EVALUATION OF PROPOSED FAULT TOLERANT PARALLEL FFT USING THE PARITY-SOS-ECC TECHNIQUE WITH ADDERS *Half Adder:*

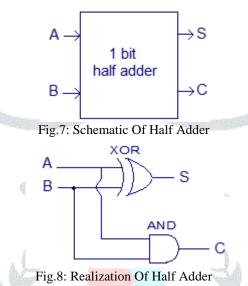

It is a combinational circuit that performs the addition of two bits, this circuit needs two binary inputs and two binary outputs. The simplified Boolean function from the Half adder truth table:

## $S = A \bigoplus B(Exclusive OR)$

#### C = A.B(AND)

The main disadvantage of this circuit is that it can only add two inputs and if there is any carry it is neglected. Thus, the process is incomplete. To overcome this difficulty Full Adder is designed. While performing complex addition, there may be cases when you have to add two 8 bit bytes together. This can be done with the help of Full Adder.

| Inputs |     | Outputs |   |  |  |

|--------|-----|---------|---|--|--|

| А      | в   | s       | С |  |  |

| 0      | 0   | 0       | 0 |  |  |

| 1      | 0   | 1       | 0 |  |  |

| 0      | 1 1 |         | 0 |  |  |

| 1      | 1   | 0       | 1 |  |  |

Fig.6: Truth Table

#### Full Adder:

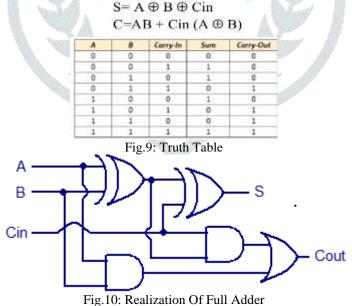

Full Adder is a combinational circuit that performs the addition of three bits (two significant bits and previous carry). It consists of three inputs and two outputs, two inputs are the bits to be added, the third input represents the carry form the previous position. The full adder is usually a component in a cascade of adders, which add 8, 16, etc., binary numbers.

The simplified Boolean function from the Full adder truth table:

#### **PERES GATES:**

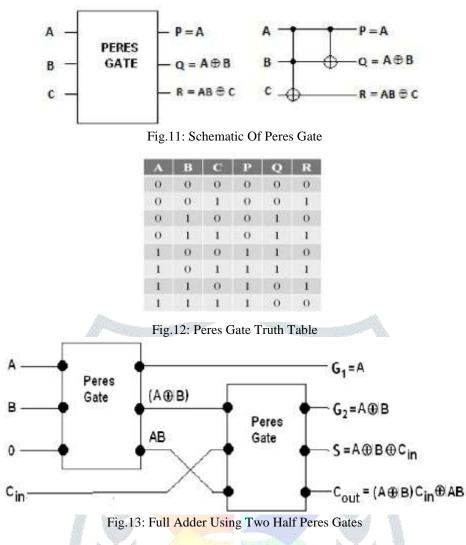

Fig 11 shows a 3\*3 Peres gate. The input vector is I (A, B, C) and the output vector is O (P, Q, R). The output is defined by P = A, Q = A $\oplus$  B and R=AB  $\oplus$  C. Quantum cost of a Peres gate is 4. In the proposed design Peres gate is used because of its lowest quantum cost.

A full- adder using two Peres gates is as shown in fig 13. The quantum realization of this shows that its quantum cost is 8 two Peres gates are used.

A single 4\*4 reversible gate called PFAG gate with quantum cost of 8 is used to realize the multiplier.

#### IV. RESULTS AND DISCUSSION

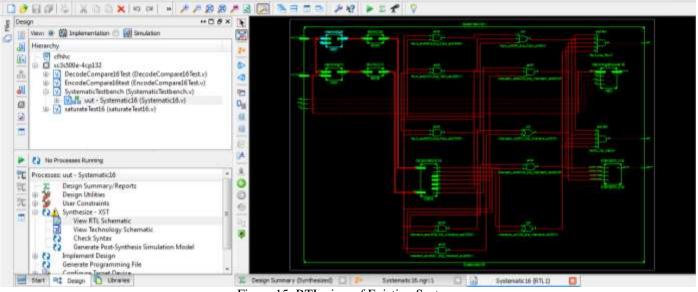

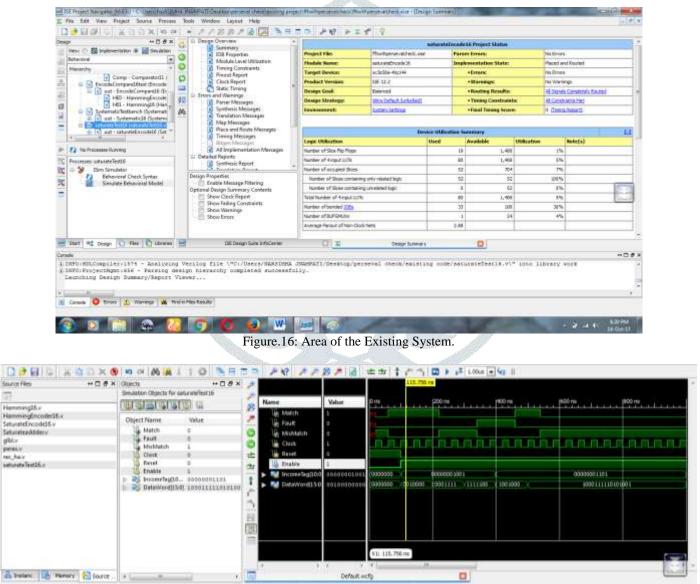

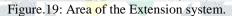

In this existing system, matching and mismatching condition using the single precision error corrections we will check the error if error is occurred then it has a fault and no error then it has no faults.

| lew Layout Help                                                                                                                                     |                                                                                          |                           | a a   4 .      | the strong  | 16 1 |                                 | -14 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|---------------------------|----------------|-------------|------|---------------------------------|-----|

| Objects + D = 0<br>Simulation Objects for saturateTest IS                                                                                           |                                                                                          | Value                     |                | E6.146 ms   |      | 600 ms                          |     |

| Object Name Value<br>Match 0<br>Fault 0<br>MinMatch 1<br>Clock 0<br>Reset 0<br>Faults 1<br>DisomeTag[10. 0000001101<br>DataWord[150] Isoo1111101010 | Ig Fault Ig fault Ig hichtatch Ig hichtatch Ig Reset Ig Reset Ig Fault Ig Reset Ig Fault | Statistics and the second | 0000000        | 000000 5001 |      | 00000001102<br>1000111110301001 |     |

|                                                                                                                                                     |                                                                                          | e b                       | X1: 114.146 rs |             |      |                                 |     |

Figure.14: Simulation Results of Existing System.

61

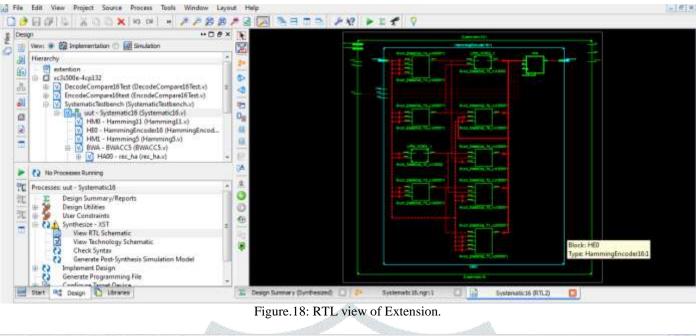

Figure.15: RTL view of Existing System.

Figure.17: Simulation Results of Extension.

| **************************************                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | G                                          | III Design Overview                                                                                                     |                                                      |                                   | saturatefine         | ode16 Project State             |                 |                                                   |              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|-----------------------------------|----------------------|---------------------------------|-----------------|---------------------------------------------------|--------------|

| view 🗇 🔯 Inglementation 🕷 🚮 Semulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -                                          | 10B Properties                                                                                                          | Project File:                                        | Automation alone                  | 1                    | arser Errora                    |                 | to brank                                          |              |

| Behaviotal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2                                          | Madule Level Okiaation Timing Constraints Prince Report Okick Report Static Timing Prince and Warning Prince Messages   | Flodule Name:                                        | naturateDricode 18                | Ir                   | uplementation State             | -               | Reced and                                         | d Routed     |

| Herarchy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0                                          |                                                                                                                         | Target Device:                                       | xc3e50a-4to144                    | 1                    | +ferors:                        |                 | No Emare                                          |              |

| extension                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Q                                          |                                                                                                                         | Product Version IIE 12-2                             |                                   | 1                    | •Warningsi<br>•Routing Resultsi |                 | 1 Warning (Lnew)<br>All Signah Completing Routest |              |

| II- DecodeCompare15Text (DecodeCo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                            |                                                                                                                         | Design Gool                                          | Balanced                          |                      |                                 |                 |                                                   |              |

| EncodeCompare10est (EncodeCom<br>SystematicTextbench: (EncodeCom | 霜                                          |                                                                                                                         | Design Strategy:                                     | Minx Default Larisched            | X I                  | +Timing Constru                 | inta:           | 4 Comb                                            | Arrita Photo |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Synthesis Messages<br>Translation Messages | Environment: System Selling                                                                                             |                                                      | 1                                 | +Final Timing Score: |                                 | (Cimme Harport) |                                                   |              |

| (2) Har Processes Running                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                            | Bitger Messages                                                                                                         | Number of Sice File Floors                           |                                   |                      | 19 1                            | 408             | 1%                                                |              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                            | Detailed Reports                                                                                                        | Number of 4 your 11/75                               |                                   | -                    |                                 | 408             | 3%                                                |              |

| Processes saturateTest36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Synthesis Report                           | Number of unused Scen                                                                                                   |                                                      |                                   | 52                   | 704                             | 7%              |                                                   |              |

| Behavioral Check Syntax                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | - 3                                        | Design Properties<br>Choose I Finable Message Filtering<br>Optional Design Summary Contents<br>Show Folking Constraints | Number of Sloet contain                              | an ach contributions              |                      | 12                              | 12              | 100%                                              |              |

| Simulate Behavioral Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | - 1                                        |                                                                                                                         | International test in the second state of the second | Construction of the second second |                      | 14                              |                 | 0%                                                | Law.         |

| Development of the second s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                            |                                                                                                                         | Number of Silves containing unrelated lags:          |                                   |                      | -                               | 52              |                                                   | 3            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                            |                                                                                                                         | Total Number of 4 input UUTs                         |                                   | -                    | - CT-1                          | 408             | 5%                                                | 12.4         |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Show Warnings<br>Show Errors               | Number of bondled 280                                                                                                   |                                                      | -                                 | 50                   | 138                             | 30%             |                                                   |              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                            | Paumber of BUFGMUNa                                                                                                     |                                                      |                                   | 1                    | 24                              | 4%              |                                                   |              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | and a structure of the second              |                                                                                                                         | Average Panaut of Non-Clock Nets                     |                                   |                      | 30                              |                 |                                                   |              |

#### **IV. CONCLUSION**

In this task, the assurance of parallel FFTs against delicate blunders has been examined utilizing two proposed strategies. The proposed procedures depend on consolidating a current ECC approach with the conventional SOS check. The SOS checks are utilized to distinguish and find the blunders and a straightforward equality FFT is utilized for revision. The discovery and area of the mistakes should be possible utilizing a SOS check for each FFT or on the other hand utilizing an arrangement of SOS watches that shape an ECC .The proposed methods have been assessed both as far as usage many-sided quality and blunder identification abilities.

The current technique is the repetitive strategy which is utilized to distinguish single blunder and redresses the single mistake blame. The second system or the equality SOS procedure is the parseval check technique, for the most part it is the aggregate of squares as the contribution of FFT and whole of squares of as the yield of FFT must be equivalent at that point there is no blame in FFT, when there is no equivalent esteems then it is thought to be blame in FFT. This technique distinguishes different blame FFTs however, redresses just single blame at once. At that point, the second procedure or the equality SOS-ECC method is the mix of blunder rectification code and parseval check. This strategy additionally has the inconvenience of rectifying single mistake. The principle advantage over the equality SOS blame tolerant parallel FFTs method is to diminish the quantity of SOS checks required. In this strategy, the parseval check is utilized to adjust the blame FFT. At once single mistake can be recognized and amended as a result of this issue it has disservice of time delay. The proposed equality SOS-ECC method comes about demonstrates that the less intricacy, less region, less deferral and less power contrasted with the equality SOS strategy.

The after effects of equality SOS-ECC method demonstrates that best regarding usage unpredictability. Regarding blunder assurance, blame infusion tests demonstrate that the ECC method can recuperate every one of the mistakes that are out of the resilience run. The blame scope of the equality SOS and the equality SOS-ECC procedures is  $\sim$ 99.9% when the resilience level for SOS check is 1.

#### V. FUTURE SCOPE

By utilizing the proposed procedures, the security of parallel FFT should be possible in DSP frameworks. The mistake recognition and rectification is finished by applying ECC's to parallel FFT's yields. The viability i.e., circuit overheads and single blame amendment is examined by utilizing contextual analysis. The execution is enhanced as far as deferral is diminished.

The future extent of this venture should likewise be possible for FIR or IIR channels rather than FFT. Another augmentation is as opposed to utilizing hamming codes another blunder redress codes can be utilized.

Blame tolerant parallel channel can be actualized for additionally required examples.

#### REFERENCES

[1] N. Kanekawa, E. H. Ibe, T. Suga, and Y. Uematsu, Dependability in Electronic Systems: Mitigation of Hardware Failures, Soft Errors, and Electro-Magnetic Disturbances. New York, NY, USA: Springer-Verlag, 2010.

[2] R. Baumann, "Delicate blunders in cutting edge PC frameworks," IEEE Des. Test Comput., vol. 22, no. 3, pp. 258–266, May/Jun. 2005.

[3] M. Nicolaidis, "Plan for delicate blunder relief," IEEE Trans. Gadget Mater. Rel., vol. 5, no. 3, pp. 405–418, Sep. 2005.

[4] A. L. N. Reddy and P. Banerjee, "Calculation based blame discovery for flag preparing applications," IEEE Trans. Comput., vol. 39, no. 10, pp. 1304–1308, Oct. 1990.

[5] T. Hitana and A. K. Deb, "Crossing over simultaneous and non-simultaneous blunder identification in FIR channels," in Proc. Norchip Conf., Nov. 2004, pp. 75–78.

[6] S. Pontarelli, G. C. Cardarilli, M. Re, and A. Salsano, "Thoroughly blame tolerant RNS based FIR channels," in Proc. fourteenth IEEE Int. On-Line Test Symp. (IOLTS), Jul. 2008, pp. 192–194.

[7] B. Shim and N. R. Shanbhag, "Vitality proficient delicate mistake tolerant computerized flag handling," IEEE Trans. Large Scale Integr. (VLSI) Syst., vol. 14, no. 4, pp. 336–348, Apr. 2006.

[8] E. P. Kim and N. R. Shanbhag, "Delicate N-particular excess," IEEE Trans. Comput., vol. 61, no. 3, pp. 323-336, Mar. 2012.

[9] J. Y. Jou and J. A. Abraham, "Blame tolerant FFT systems," IEEE Trans. Comput., vol. 37, no. 5, pp. 548–561, May 1988.

[10] S.- J. Wang and N. K. Jha, "Calculation based adaptation to non-critical failure for FFT systems," IEEE Trans. Comput., vol. 43, no. 7, pp. 849–854, Jul. 1994.

[11] A. Sibille, C. Oestges, and A. Zanella, MIMO: From Theory to Implementation. San Francisco, CA, USA: Academic, 2010.

[12] G. L. Stüber, J. R. Barry, S. W. McLaughlin, Y. Li, M. A. Ingram, and T. G. Pratt, "Broadband MIMO-OFDM remote correspondences," Proc. IEEE, vol. 92, no. 2, pp. 271–294, Feb. 2004.

[13] Zhen Gao, Pedro Reviriego, Zhan Xu, Xin Su, Ming Zhao, Jing Wang, and Juan Antonio Maestro, "Fault Tolerant Parallel FFTs Using Error Correction Codes and Parseval Checks" IEEE (VLSI) SYSTEMS, VOL. 24, NO. 2, FEBRUARY 2016.

[14] P. Reviriego, S. Pontarelli, C. J. Bleakley, and J. A. Maestro, "Zone proficient simultaneous blunder location and redress for parallel channels," IET Electron. Lett., vol. 48, no. 20, pp. 1258–1260, Sep. 2012.

[15] Z. Gao et al., "Blame tolerant parallel channels in light of mistake rectification codes," IEEE Trans. Large Scale Integr. (VLSI) Syst., vol. 23, no. 2, pp. 384–387, Feb. 2015.

[16] R. W. Hamming, "Blunder identifying and mistake revising codes," Bell Syst. Tech. J., vol. 29, no. 2, pp. 147-160, Apr. 1950.

[17] P. Reviriego, C. J. Bleakley, and J. A. Maestro, "A novel simultaneous blunder location method for the quick Fourier change," in Proc. ISSC, Maynooth, Ireland, Jun. 2012, pp. 1–5.

[18] Robert C. Baumann, Fellow, IEEE ,"Radiation-Induced Soft Errors in Advanced Semiconductor Technologies", VOL. 5, NO. 3, SEPTEMBER 2005.

#### **AUTHORS BIO-DATA:**

Dr.D.Nageshwar Rao received the B.E. in Electronic Engineering from Shyamlal College of Engineering, SRTMU Nanded, in 1999 and M.Tech with specialization DSCE from JNTU College of Engineering, JNTU HYD in 2004. He completed Ph.D. at GITAM University, Vishakhapatnam in 2014. His doctoral research is directed towards the design of a low voltage, low power VLSI analog circuits. His area of research is Low power VLSI, Image Processing & Video Processing. Presently he is working as Professor, Head of the Department, ECE, in TKR College of Engineering & Technology, Meerpet, Hyderabad.

A.SHANKARAIAH, studying M.Tech degree in VLSI, Electronics and Communication Engineering from Jawaharlal Nehru Technological University for the academic year 2015-2018.