# Design of an Efficient Multiplier Using15-4 Compressor for DSP Applications

# BOLLAM SWATHI<sup>1</sup>, D. NAGASUDHA<sup>2</sup>

<sup>1</sup>PG Scholar, Dept of DS & CE, JNTU College of Engineering and Technology, Karimnagar, TS, India. <sup>2</sup>Assistant Professor, Dept of DS & CE, JNTU College of Engineering and Technology, Karimnagar, TS, India.

**Abstract:** In this paper, we introduce a new idea for multiplication. A 16X16 bit multiplier is designing with the assist of 15:4 compressors in that 5:3compressors as a central unit. The existing approximated multipliers perform the multi operand carry save addition. These occupied larger space and high delay. The goal behind our proposition is minimizing the utilization of power required and expanding the pass rate. This proposed expertise is extensively utilized in image and video processing applications to enhance the contrast of an image.

Keywords: Approximate 5-3 Compressor, Approximate15-4compressor, Multiplier, Image Processing, Higher Order Compressor.

# I. INTRODUCTION

Advanced multipliers are among the most basic math utilitarian units in numerous applications, for example, the Fourier change, discrete cosine changes, and computerized sifting. The throughput of these applications relies upon multipliers, and if the multipliers are too moderate, the execution of whole circuits will be lessened. To diminish the calculation mistake, numerous remuneration procedures were displayed for exhibit multipliers. There is an evidently tradeoff amongst exactness and equipment intricacy. As of late, remuneration works have been expanding centered around diminishing the truncation mistake on the Booth multiplier. Multipliers have been imperative since the presentation of the advanced PCs. Duplication happens every now and again in Digital Signal Processing (DSP) frameworks, correspondence frameworks and other Application Specific Integrated Circuits (ASICs). Due to the centrality of duplication in logical and designing calculations, this territory has gotten much consideration in the previous decades which have prompted various execution strategies for increase. The immense assortment of use territories for multipliers displays distinctive prerequisites for speed, region, control utilization and different determinations. In view of these prerequisites, which are forced from the framework that the multiplier will work in, various qualities of the multiplier will be given diverse needs. It is the planner's errand to pick a reasonable duplication calculation and usage strategy as per these needs. Customarily, the outline needs have been given to speed and zone. In any case, the quick advancement of computerized frameworks has caused a noteworthy change in perspective in the previous years. Presently, different parameters like low-power, flexibility, testability and unwavering quality have gone into the play. Power scattering has turned into a critical limitation in the outline of advanced frameworks. This is significantly more vital for battery-controlled applications where the vitality spending plan is to a great degree constrained. Low-control configuration has turned into another zone in VLSI innovation and power-mindful outline is unavoidable in the new Electronic Design Automation (EDA) tools. Multipliers are by and large computationally substantial circuit parts. Fundamentally an expansive number of transistors with high progress exercises must be dedicated to play out the increase. More transistors with high progress exercises mean more inner capacitance, more general exchanging and thus more power dissemination. Likewise the aggregate spillage current is required to be vast in a multiplier in view of its huge dynamic territory. Multipliers are among the primary benefactors of region and power utilization in a DSP framework and, all the more vitally, they are typically put in the basic ways of such frameworks. All through this postulation, an outline approach is proposed for diminishing the dynamic and static power dissemination in parallel multipliers. It is accepted that the multiplier will work continuously frameworks where fast is basic. Thusly, among the assortment of execution strategies, fast parallel usage techniques are tended to. The streamlining strategy is an interconnection reordering calculation in light of the info information qualities. It is appropriate straightforwardly on all full-snake based parallel multipliers. With a few changes the advancement strategy is relevant for lion's share of the diminishment plans. The advancement just alters the interconnects between rationale doors and the rationale entryways and the design stays unaltered. Broadly utilized rapid duplication systems, concentrating chiefly on the parts that will be tended to in the accompanying sections. More intricate dialogs about the increase methods are given, Moreover, the discourses of this section are just restricted to settled point multipliers. Truth be told, the drifting point multipliers comprise of a settled point multiplier for the huge, in addition to fringe and bolster hardware to manage the examples and unique qualities. In this way the enhancement strategies talked about in the accompanying sections are likewise relevant for gliding point administrators.

Settled point duplication includes two essential advances: creating halfway items (PPs) and collecting the produced PPs. The different increase plans contrast in the age or potentially amassing strategies. Thusly, accelerate in the increase procedure is accomplished in two different ways: creating less number of PPs in the initial step or quickening their collection in the second step. The least complex plan for increase, known as move and-include plot, comprises of cycles of moving and including with equipment or programming control circles. The paper is sorted out as takes after. Plans of approximate5-3 blowers are expounded in area II. Plan of 15-4 blower utilizing 5-3 blower is portrayed in section III. Segment IV portrays outline of  $16 \times 16$  multiplier.

Result analysis is portrayed in area V. Picture preparing application using proposed multiplier is given in segment VI. Finally, the conclusion is displayed.

#### **II. RELATED WORK**

ParagKulkarni, Puneet Gupta, Miloš D. Ercegovac et al., proposed a novel multiplier engineering with tunable blunder qualities that influences an adjusted wrong 2x2 multiplier as its building square. Our off base multipliers accomplish a normal power sparing of 31.78% – 45.4% over relating precise multiplier plans, for a normal blunder of 1.39%–3.32%. We contrast our design and different methodologies, for example, voltage scaling, for presenting mistake in a multiplier. Utilizing picture sifting and JPEG pressure as test applications we demonstrate that our design can accomplish 2X - 8X better Signal-Noise-Ratio (SNR) for a similar power investment funds when contrasted with late voltage over-scaling based power-blunder tradeoff techniques. We anticipate the multiplier control investment funds to greater outlines featuring the way that the advantages are firmly plan subordinate. We contrast this circuit-driven approach with control quality tradeoffs with an unadulterated programming adjustment approach for a JPEG illustration. Not at all like ongoing outline for-mistake approaches for math rationale, have we likewise improved the plan to take into account remedy activity of the multiplier utilizing an adjustment unit, for non-blunder flexible applications which share the equipment asset. D. Radhakrishnan, A.P. Preethy et al., proposed novel CMOS 4-2 blower utilizing pass rationale is exhibited in this paper. A XOR-XNOR blend entryway is utilized to fabricate the circuit while absolutely wiping out the utilization of inverters. Improving the execution of skimming point tasks is imperative for current elite chip. In such manner fast augmentation is getting to be one of the key tasks in RISCs, ongoing picture and flag preparing, constant discourse acknowledgment, illustrations quickening agents et cetera, because of the expanding request from media applications. Due to their high computationally concentrated preparing prerequisites in these applications, low-control scattering is turning into an essential plan objective in numerous convenient video, sounds and registering frameworks. The aggregate power scattering has been chopped down to a base while giving the full yield voltage swing at all hubs in the circuit. Moreover, the total circuit is executed with an absolute minimum of 28 transistors.

RiyaGarg, SumanNehra, B. P. Singh et al., discussed that majority of the VLSI circuits utilized adders as a significant part, since they shape the base component of every single number juggling capacity. Expanding interest for convenient types of gear requires zone and power effective VLSI circuits. Paper presents 4-2 blower utilizing two distinctive 8T full viper outlines. The point of this paper is to lessen the power utilization of 4-2 blower without trading off the speed and execution. Full snake is basic unit in different circuits, particularly, in performing math activities, for example, blowers, comparators, equality checkers, multipliers and so forth. It is the core of numerous other valuable activities; for example, subtraction, duplication, division, exponentiation, address figuring and can altogether impact the general achievable exhibitions of the framework. All pre-design and post-format recreations have been performed at 45nm innovation on Tanner EDA apparatus rendition 12.6 and thought about as far as power utilization, control defer item (PDP) over different info voltages, temperatures and frequencies. Suresh Cheemalavagu, Pinar Korkmaz, Krishna V. Palem et al., proposed that subject of this examination is the probabilistic inverter, pervasive to the outline of advanced frameworks, whose conduct is rendered probabilistic by clamor. Abridged through the idea of a vitality likelihood relationship for inverters in light of AMI 0.5µm and TSMC 0.25µm procedures, we quantitatively demonstrate that huge vitality funds are conceivable when a probabilistic inverter is exchanged with likelihood 1/2 , andthat these reserve funds increment exponentially as p is brought down. We likewise quantitatively demonstrate that for a settled p, expanding the clamor RMS has the impact of expanding vitality scattering quadratically. By and large, we allude to these two actualities as the vitality likelihood laws administering probabilistic CMOS switches these laws constitute the principal commitment of this work. Besides, we additionally display a commonsense acknowledgment of a probabilistic inverter in a promptly accessible TSMC 0.25µm innovation.

#### **III. EXISTING SYSTEM**

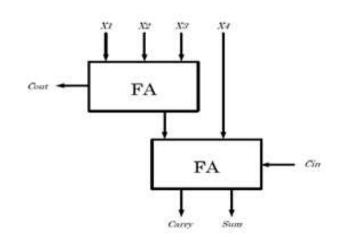

The principle objective of either multi-operand convey spare expansion or parallel increase is to decrease n numbers to two numbers; in this manner, n-2 blowers (or n-2 counters) have been generally utilized as a part of PC number-crunching. A broadly utilized structure for pressure is the 4-2 blower; a 4-2 blower can be executed with a convey bit between contiguous cuts. The convey bit from the situation to the privilege is signified as cin while the convey bit into the higher position is meant as cout. The two yield bits in positions I and I + 1 are likewise alluded to as the aggregate and convey individually. The normal usage of a 4-2 blower is refined by using two full-snake (FA) cells.

#### **IV. PROPOSED METHOD**

Expansion and duplication are broadly utilized activities in PC math; for expansion full-snake cells have been widely broke down for estimated processing. It has looked at these adders and proposed a few new measurements for assessing surmised and probabilistic adders concerning brought together figures of legitimacy for outline appraisal for estimated processing applications.

#### Fig.1.

For each contribution to a circuit, the blunder remove (ED) is characterized as the number juggling separation between a mistaken yield and the right one. The mean blunder remove (MED) and standardized mistake separate (NED) are proposed by considering the averaging impact of different data sources and the standardization of various piece adders. The NED is about invariant with the measure of a usage and is in this way valuable in the unwavering quality evaluation of a particular plan. The tradeoff amongst accuracy and power has likewise been quantitatively assessed. Be that as it may, the outline of surmised multipliers has gotten less consideration. Augmentation can be thought as the rehashed aggregate of fractional items; in any case, the direct use of estimated adders when outlining a rough multiplier isn't practical, on the grounds that it would be exceptionally wasteful as far as exactness, equipment intricacy and other execution measurements. A few rough multipliers have been proposed in the writing. The greater part of these outlines utilize a truncated duplication technique; they evaluate the minimum huge segments of the halfway items as a consistent. In an uncertain cluster multiplier is utilized for neural system applications by excluding a portion of the slightest critical bits in the fractional items (and accordingly evacuating a few adders in the exhibit). A truncated multiplier with a redress steady is proposed. For an×n multiplier, this outline computes the whole of the n+k most huge sections of the halfway items and truncates the other n-k segments. The n+k bit result is then adjusted to n bits. The decrease mistake (i.e. the blunder created by truncating then-k slightest noteworthy bits) and adjusting mistake (i.e. the mistake produced by adjusting the outcome to n bits) are found in the following stage. The adjustment steady (n+k bits) is chosen to be as close as conceivable to the evaluated estimation of the whole of these mistakes to lessen the blunder remove. A truncated multiplier with consistent redress has the greatest blunder if the incomplete items in the n-k minimum huge segments are every one of the ones or each of the zeros. A variable amendment truncated multiplier has been proposed in [6]. This technique changes the revision term in light of segment n-k-1. In the event that every single halfway item in columnn-k-1 are one, at that point the remedy term is expanded. So also, if every single incomplete item in this section are zero, the amendment term is diminished.

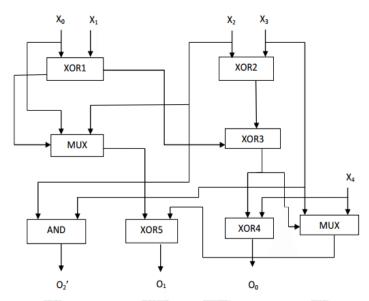

#### A. Designs Of Approximate 5-3 Compressors

In this section, four designs of a 5-3 approximate compressor are presented. 5-3 compressor has five primary inputs (X0; X1; X2; X3; X4) and three outputs (O0; O1; O2). This compressor uses the counter property. Output of the compressor depends on number of ones present at input. This proposed compressor also called as 5-3 counter. In this paper, we have called this module as a compressor because this module compresses five bits into three bits. We have chosen 5- 3 compressors because it is a basic module for 15-4 compressor. Error rate and error distance of each design are considered.

**Design 1:** In this design, initially output O2 of 5-3 compressor is approximated. Logical AND between inputs X3 and X2 matches with accurate output O2 of the conventional 5-3 compressor with an error. The following expressions show design 1 of 5-3 approximate compressor. Fig.2 shows the design1 of approximate 5-3 compressor.

$$O_2' = X_3 \bullet X_2 \tag{1}$$

Fig.2. Approximate 5-3 compressor (Design 1).

$$O_{2} = (X_{0} \bullet (\sim (X_{0} \oplus X_{1})) + X_{2} \bullet (X_{0} \oplus X_{1})) + X_{2} \bullet (X_{0} \oplus X_{1})) + X_{4} \bullet (X_{0} \oplus X_{1} \oplus X_{2} \oplus X_{3})) + X_{4} \bullet (X_{0} \oplus X_{1} \oplus X_{2} \oplus X_{3})) + (X_{2} \bullet (X_{0} \oplus X_{1})) + (X_{2} \bullet (X_{0} \oplus X_{1}))) \oplus (X_{3} \bullet (\sim (X_{0} \oplus X_{1} \oplus X_{2} \oplus X_{3})))) + (X_{4} \bullet (X_{0} \oplus X_{1} \oplus X_{2} \oplus X_{3} \oplus X_{4})))$$

$$O_{0} = X_{0} \oplus X_{1} \oplus X_{2} \oplus X_{3} \oplus X_{4}$$

(2)

(3)

(3)

$$O'_{0} = [(X_{3} \bullet X_{2} \bullet (\sim X_{1}) \bullet (\sim (X_{0})) \\ + ((\sim X_{4}) \bullet X_{3} \bullet X_{2} \bullet (X_{1} \oplus X_{0})) \\ + (X_{4} \bullet X_{1} \bullet X_{0} \bullet (X_{2} \oplus X_{3}))]? \\ (\sim (X_{3} \bullet X_{2})) : (X_{4} \oplus X_{3} \oplus X_{2} \oplus X_{1} \oplus X_{0})$$

(5)

Finally, O1 is kept as original expression. O2 replaced by O2' and O0 is replaced by O00 to get the minimum error distance. Maximum error distance is 4 for only one input pattern (i.e input number 12) and in the remaining five cases; the error distance is either +3 or -3. Critical path of this design is higher than accurate design. This design has additional logic gates such as one MUX and one XOR in critical path when compare to accurate design.

**Design 2:** In this design, O2, O1 are approximated and O0 is kept as the same as original expression. Error distance of all the error cases is either -2 or +2. From the truth table, it can be noted that when O2 alone is replaced with O2 in a 5-3 compressor. Similarly, When compared with the O1 output of the 5-3 compressor. Expression for O2 and O1 are modified to get the minimum error distance the output of the compressor differs only in eight input cases. Table 2 shows all error cases and the error distance between actual and approximated outputs. In this design, the critical path is between input X0 and output O0. Four XOR gates are involved in the critical path. This design has least critical path than other proposed designs. Fig. 3 shows the logic diagram of design 2 approximate 5-3 compressor.

Fig.3. Logic diagram of design 2 approximate 5-3 compressor.

$$O'_{2} = X_{4} \bullet [X_{0} \bullet (\sim (X_{0} \oplus X_{1})) + (X_{2} \bullet (X_{0} \oplus X_{1}))]$$

(6)

**Design 3:** In this design, only output O1 is replaced by O1<sup>1</sup>. Expression for O1<sup>1</sup> is given below. Remaining outputs of the compressor (O0 and O2) are kept same as original expression. The error distance is either +2 or -2. In this design, the critical path has three XOR, two AND, one OR and one inverter gates.

$$O_1' = X_4 \oplus [X_0 \bullet (\sim (X_0 \oplus X_1)) + (X_2 \bullet (X_0 \oplus X_1))]$$

$$(7)$$

$$O_1' = X_4 \oplus [X_0 \bullet (\sim (X_0 \oplus X_1)) + (X_2 \bullet (X_0 \oplus X_1))]$$

(8)

**Design 4:** In this design, output of O1 expression is approximated  $(O1^{1})$  and expressions for O0 and O2 are kept as an accurate. Expression for approximated  $O1^{1}$  is given below.

$$O_1' = X_2 \oplus X_3 \tag{9}$$

Only one X-OR gate is utilized to get approximated  $O1^1$ . The length of the critical path is same as design 3. This consumes the lesser area and power than the other proposed 5-3 compressor designs. The maximum error distance is either +2 or -2.

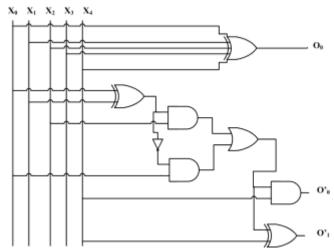

#### **B. Design Of 15-4 Compressor**

This area depicts the plan of 15-4 blower utilizing estimated 5-3 blowers. The 15-4 blower was proposed as appeared in fig.3. This blower has fifteen information sources (X0 - X14) and it produces four yields (O0 - O3). This blower has five full adders at first stage, two 5-3 blowers in second stage and last stage has parallel snake. Each full viper gets three essential data sources and it creates "Aggregate" and "Convey". "Total" of every single full viper is given to the 5-3 blower. So also, "Convey" of every full snake is given to another 5-3 blower. Yields of the 5-3 blowers are given to the parallel viper. Parallel viper is utilized to produce the last yield. In surmised 15-4 blower, rather than utilizing exact 5-3 blowers, we have utilized proposed estimated 5-3 blower are proposed. 5-3 blowers are utilized as a part of initial three outlines of rough 15-4 blower which utilizes the plan 1, 2 and 3 of proposed estimated 5-3 blower. Plan 1 and outline 4 of proposed surmised 5-3 blower are utilized as a part of plan 4 of 15-4 blower. Outline 1 rough 5-3 blower is utilized to deal with "convey" signals since yield "convey" has more weight age than "aggregate". In addition, a pass rate of plan 1 blower is higher than outline 4. Outline 4 estimated 5-3 blower is utilized to deal with aggregate signs.

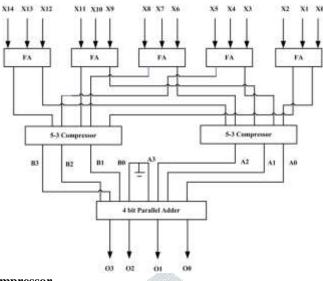

#### C. Multiplier Design

In this segment, plan of  $16 \times 16$  multiplier is presented. Four rough multipliers are composed utilizing the proposed four 15-4 blowers. Moreover, one accurate multiplier and four other estimated multipliers are considered. Inexact multipliers utilizing the proposed. Inexact 15-4 blowers are contrasted and the accurate  $16 \times 16$  multipliers with exact 15-4 compressors and additionally with different multipliers outlined utilizing different other approximate blowers. Fig.4 demonstrates the plan of  $16 \times 16$  piece multiplier utilizing 15-4 blower where, each dot represents one halfway item. Six 15-4 blowers are used to outline one multiplier in the halfway item decrease and finally four multipliers are composed.

## Fig.4. Design of accurate 15-4 compressor.

In figure, rectangular boxes show the utilization of 15-4 and 4-2 blower in the multiplier. 15-4 blowers are utilized as a part of the multiplier from thirteenth segment onwards. Segment number 13of the multiplier has just thirteen fractional items. Two zeros are included that section to make utilization of the 15-4 compressor. Similarly, one "0" is included fourteenth segment. Alongside 15-4compressors in the multiplier other precise blower like4-2 and half, full adders are utilized for fractional item reduction. Approximate blowers are utilized as a part of thirteenth, fourteenth and 15thcolumn of multipliers. Utilization of rough blowers' deepest huge part would deliver a bigger mistake rate. Design1 of 15-4 estimated blower is utilized as a part of multiplier 1.Similarly, plan 2, 3 and 4 of 15-4 inexact compressors are utilized as a part of multiplier 2, 3 and 4 separately. In accurate multiplier, all exact 15-4 blowers are utilized along with accurate 3-2 and 4-2 blowers. Exact 4-2 blowers, half and full adders are utilized in second and third phase of incomplete item decrease tree. In last stage, parallel adders are utilized to figure the last outcome.

| uns paper i                           | .5 d5 5110 W | II III UCIIO | w 1 155.5 | 10 7.    |          | 1.1      | 80      | 100         |          |

|---------------------------------------|--------------|--------------|-----------|----------|----------|----------|---------|-------------|----------|

|                                       |              |              |           |          |          |          |         | 4,188.350 m |          |

| Name                                  | Value        | 1,500 ns     | 2,000 ns  | 2,500 ns | 3,000 ns | 3,500 ns | 4,000 r | 5           | 4,500 ns |

| 🕨 🕌 a(150)                            | 10           | 65535        |           |          | 1        | 3        |         | 10          |          |

| 🕨 🕌 bj15kij                           | 500          | 65535        |           |          | i        | 17       |         | 500         |          |

| • • • • • • • • • • • • • • • • • • • | 5000         | 4943625      | 2         | i        | 92       | 01       |         | 5000        |          |

| 🕨 🙀 p[255:0]                          | 140737498388 | >            | 21474     | 36485    |          | <i>,</i> | 1       | 1/31-88388  | 9600     |

| 🕨 🙀 (4721)                            | 2            | >            | 11        | 6        |          | <i>,</i> |         | >           |          |

| ▶ 🕌 j[230]                            | 1            | 16776924     |           |          | 16       | 004      |         | 1           |          |

|                                       |              |              |           |          |          |          |         |             |          |

|                                       |              |              |           |          |          |          |         |             |          |

#### V. SIMULATION RESULTS

Simulation results of this paper is as shown in bellow Figs. 5 to 9.

Fig.5. Accurate Design.

| Name            | Value        | 0us | 105           | 2us         | 3us     | 415           | Sus |

|-----------------|--------------|-----|---------------|-------------|---------|---------------|-----|

| 🕨 🕌 a(150)      | 10           | Z   | 65535         | 5           | 273     | 11            |     |

| bitsej          | 501          | 200 | 65535         | <u> </u>    | 337     | 500           |     |

| \$10            | 5000         | Y   | 4294651905    | 25          | 247649  | 5000          |     |

| 🕨 🙀 p(255d)     | 140737488388 | X   | >             | 21474836485 | >       | 1407374883880 |     |

| 🕨 🙀 (4721)      | ×            | Y   | $\rightarrow$ | 1036        | - >     | $\rightarrow$ |     |

| ► <b>1</b> (BI) | 1            | Y   | 16773138      | 0           | 3158015 | 1             |     |

# Fig.6. Approximated Design 1.

| Name            | Value        | 0us | lus        | 2us         | 3us     | Hus .         | 5us |

|-----------------|--------------|-----|------------|-------------|---------|---------------|-----|

| 🕨 🕌 aj15:0j     | 10           | 2   | 65535      | 5           | 273     | 10            |     |

| <b>b</b> [15:0] | 500          | 1   | 65535      | 5           | 337     | 500           |     |

| 🕨 🕌 tj31.0j     | 5000         | X   | 4294651905 | 25          | 83809   | 5000          |     |

| ▶ 🙀 p[255:0]    | 140737499388 | X   | >          | 21474836485 | >       | 1407374883880 |     |

| 🕨 💐 d(472:1]    | <b>\$</b> 0  | X   | >          | 1036        |         | >             |     |

| 0.651 🙀 📢       | 1            | X   | 16773138   | 0           | 1052672 | 1             |     |

# Fig.7. Approximated Design 2.

|              |         |     |            |             |       | 3.6316 | 00 us            |     |

|--------------|---------|-----|------------|-------------|-------|--------|------------------|-----|

| Name         | Value   | 0us | tus        | 2us         | Bus   | ritt   | Hus<br>Line Line | 5us |

| 🕨 🍟 aji 501j | 273     | 1   | 65535      | 5           | 273   |        | 10               | )   |

| bitstoj      | 337     | 1   | 65535      | 5           | 337   |        | 500              | )   |

| ▶ 🕌 t[31:0]  | 83809   | X   | 4294651905 | - 25        | 8380  |        | 5000             | )   |

| ▶ 🙀 p(2554)j | >       | X   | 2          | 21474836485 | >     |        | 140737488388)    | į   |

| 🕨 🙀 d4721]   | 5       | X   | >          | 1036        |       |        | $\rightarrow$    |     |

| 123.0        | 1052672 | X   | 16773138   | 0           | 10526 | 2      | 1                |     |

|              |         |     |            |             |       |        |                  |     |

NE

Fig.8. Approximated Design 3.

| Name         | Value          | Ous | 105                 | 2us         | 3us           | 4us 5         |

|--------------|----------------|-----|---------------------|-------------|---------------|---------------|

| 🕨 🕌 a(15:0)  | 273            | 1   | 65535               | 5           | 273           | 10            |

| b(150)       | 337            | 2   | 65535               | ( i         | 337           | 500           |

| ▶ 🕌 tβ1:0]   | 255841         | X   | 4294836225          | 25          | 255841        | 5000          |

| 🕨 🙀 p(255:0) | 2              | X   | >                   | 21474836485 | $\rightarrow$ | 1407374883880 |

| 🕨 🙀 (4721)   | <b>&gt;</b> :- | X   | $\langle - \rangle$ | 1036        | >             | > )           |

| (XE)]        | 3158048        | X   | 15776924            | 0           | 3158048       | 1             |

## Fig.9. Approximated Design 4.

#### **VI. CONCLUSIONS**

In this technique, we propose new plan of estimated 15-4 blower utilizing 5-3 blowers as essential module calculation is proposed to look effectively composed multiplier units. The center an incentive behind our proposed technique is the considerably higher number of adders that can be spared by the unification of each unmistakable including of a similar length, with next to no or no negative effect on the information way timing. This new approach of estimated 15-4 blower minimization is exhibited by multiplier units.

# **VII. REFERENCES**

[1] D. Liu Embedded DSP Processor Design, 1st ed.Morgan Kaufmann Publishing, 2008.

[2] K. K Parhi VLSI Digital Signal Processing Systems: Design and Implementation., 1sted. John Wiley and Sons, 1999.

[3] Y.Kim, Y.Zhang, and P. Li, "An energy efficient approximate adderwith carry skip for error resilient neuromorphic VLSI systems," in proc.of International conference on Computer-Aided Design (ICCAD), Nov.2013, pp. 130-137.

[4] A. Pishvaie, G. Jaberipur, and A. Jahanian, "Improved CMOS (4; 2)compressor designs for parallel multipliers," Computers and ElectricalEngineering, vol. 38, no. 6, pp. 17031716, Nov. 2012.

[5] D. Baran, M. Aktan, and V.G. Oklobdzija V.G. "Energy Efficient Implementation of Parallel CMOS Multipliers with Improved Compressors,"in proc. ACM/IEEE International Symposium on Low-Power Electronics and Design (ISLPED), Aug. 2010, pp. 147-152.

[6] S. Veeramachaneni, K. Krishna M, L. Avinash, S. R. Puppala, and M.B.Srinivas, "Novel Architectures for High-Speed and Low-Power 3-2, 4-2 and 5-2 Compressors," in proc. of International Conference on VLSIDesign (VLSID), Jan. 2007, pp. 324-329.

[7] R. Menon, and D. Radhakrishnan, "High performance 5: 2 compressor architectures," in proc. of IEE - Circuits, Devices and Systems, vol. 153,no. 5, Oct. 2006, pp. 447-452.

[8] A. Pishvaie, G. Jaberipur, and A. Jahanian, "High Performance CMOS(4:2) compressors," International journal of electronics, vol. 101, no. 11, pp. 1511-1525 Jan. 2014.

[9] O. Kwan, K. Nawka, and E. SwartzlanderJr, "A 16 bit by 16 bitMAC Design Using Fast 5:3 Compressor Cells," Journal of VLSI SignalProcessing, vol. 31, no. 2, pp. 77-89, July 2002.

[10] S. Mehrabi, R.F Mirzaee, S. Zamanzadeh, K. Navi, and O. Hashemipour, "Design, analysis, and implementation of partial product reduction phaseby using wide m:3 (4 m 10) compressors," Int. Journal of High Performance System Arch, vol. 4, no. 4, pp. 231-241, Jan. 2013.

[11] A. Dandapat, P.Bose, S. Ghosh, P Sarkar, and D. Mukhopadhyay, "A1.2-ns 16 x 16 bit binary multiplier using high speed compressors," WorldAcademy of Science, Engineering and Technology, vol. 39, pp. 627-632, March 2009.

[12] R. Marimuthu, M. Pradeep kumar, D. Bansal, S. Balamurugan, and P.S Mallick, "Design of high speed and low power 15-4 compressor," inproc. International Conference on Communication and Signal Processing(ICCSP), Apr. 2013, pp. 533-536.

[13] J. Liang, J. Han, and F. Lombardi, New metrics for the reliability of approximate and probabilistic adders," IEEE Trans. on Computers, vol.63, no. 9, pp. 1760 - 1771, Sep.2013.

[14] N.Zhu, W L Goh, and KiatSeng Yeo, "An enhanced low power highspeed adder for error tolerant application," in proc. of 12<sup>th</sup>InternationalSymposium on Integrated Circuits (ISIC), Nov. 2009, pp. 69 - 72.

[15] Z. Yang, A. Jain, J. Liang, J. Han, and F. Lombardi, "Approximate XOR/XNOR-based adders for inexact computing," in proc. of IEEE International Conference on Nanotechnology (IEEE - NANO), Aug. 2013, pp. 690 - 693.

[16] H. Jiang, J.Han, and F. Lombardi, "A comparative review and evaluation of approximate adders," in proc. of ACM Great Lakes Symposium on VLSI(GLSVLSI), May. 2015, pp. 343 - 348.

[17] V. Gupta, D. Mohapatra, S. P. Park, A. Raghunathan, and K. Roy, "IMPACT: IMPrecise adders for low-power approximate computing," inproc. of International Symposium on Low Power Electronics and Design(ISLPED), Aug. 2011, pp. 409 - 414.

[18] C. Liu, J. Han, and F. Lombardi, "A Low-Power, High-Performance Approximate Multiplier with Configurable Partial Error Recovery," inproc.of International Conference on Design Automation and Test in

Europe (TEST), Mar. 2014.

[19] P. Kulkarni, P. Gupta, and M. D. Ercegovac, "Trading accuracy for powerin a multiplier architecture," in Journal of Low Power Electronics, vol.7, no. 4, pp. 490501, Dec. 2011.

[20] S. Balamurugan, and P.S Mallick, "Fixed-width multiplier circuits using column bypassing and decomposition logic techniques," in International journal on Electrical Engineering and Informatics, vol. 7, no. 4, pp.655664, Dec. 2015.

[21] S. Balamurugan, S. Ghosh, Atul, S. Balakumaran, R. Marimuthu, and P.S Mallick, "Design of low power fixed-width multiplier with row by passing," in IEICE Electronics Express, vol. 9, no. 20, pp. 15681575, Oct. 2012.

[22] H.R. Mahdiani, A. Ahmadi, S.M. Fakhraie, and C. Lucas, "Bio-Inspire dimprecise computational blocks for efficient VLSI implementation of soft computing applications," in IEEE Transactions on Circuits and Systems, vol. 57, no. 4, pp. 655664, Apr. 2010.

[23] K.Y. Kyaw, W.L. Goh, and K.S. Yeo, "Low-power high-speed multiplier for error-tolerant application," in proc. of IEEE International Conference of Electron Devices and Solid-State Circuits (EDSSC), Dec. 2010, pp. 1-4.

[24] K. Bhardwaj, P.S. Mane, and J. Henkel, "Power- and area-efficient Approximate Wallace Tree Multiplier for error resilient systems," in proc.of 15th International Symposium on Quality Electronic Design (ISQED), Mar. 2014, pp. 263 - 269.

[25] M.S.K Lau, K.V. Ling, and Y.C. Chu, "Energy-aware probabilistic multiplier: design and analysis," in proc. of international conference on Compilers, architecture, and synthesis for embedded systems, Oct. 2009, pp. 281-290.

[26] R. Venkatesan, A. Agarwal, K. Roy, and A. Raghunathan, "MACACO: Modeling and analysis of circuits for approximate computing," in proc.of international conference on Compilers, architecture, and synthesis for embedded systems (ICCAD), Nov. 2011, pp. 667 - 673.

[27] F. Farshchi, M.S.Abrishami, and S.M. Fakhraie, "New approximate multiplier for low power digital signal processing," in proc. of 17 international Symposium on Computer Architecture and Digital Systems(CADS), Oct. 2013, pp. 25 - 30.

[28] H. Jiang, C. Liu, N. Maheshwari, F. Lombardi, and J. Han, "A Comparative Evaluation of Approximate Multipliers," in proc. of In International Symposium on Nanoscale Architectures (NANOARCH), Jul. 2016, pp. 191

- 196.

[29] C.-H. Lin, and I.-C. Lin, "High accuracy approximate multiplier witherror correction," in proc. of IEEE 31st International Conference on Computer Design (ICCD), Oct. 2013, pp. 33 - 38.

[30] Y. Bansal, and C. Madhu,"A novel high-speed approach for 16x16vedic multiplication with compressor adders," Computers and Electrical Engineering, vol. 49, pp. 39-49, Jan. 2016.

#### Author's Details:

**Ms. BOLLAM SWATHI** has completed B.Tech (ECE) from Sindhura College of Engineering and Technology, NTPC, Karimnagar District, JNTU University Hyderabad. Presently, she is pursuing her Masters in Digital systems and computer electronics (DS&CE) from JNTU College of Engineering and Technology, Karimnagar, Hyderabad, TS. India.

**Mrs. D. NAGASUDHA** has completed B.Tech (ECE) from SVH College of Engineering and Technology, NAGARJUNA University, Hyderabad, M.Tech (DS&CE) from JNTU Ananthapur College of engineering and technology, JNTU University, Hyderabad. Currently she is working as an Assistant Professor of ECE Department in JNTU college of Engineering and Technology, Karimnagar, Hyderabad, TS. India.