# Implementation and Analysis of 8x8 Array using 7T SRAM Cellfor Low power CMOS

Shilpi dubey M-Tech VLSI Design MPCT College Gwalior (M.P) INDIA

Pankaj Shrivastava Associate Professor, Dept. Electronics & Communication Engineering MPCT College Gwalior (M.P), INDIA

## Abstract

The majorobjective of this paper is to propose a low power 8x8 SRAM array utilize7T SRAM cell.Highdensity SRAMs employinsistentlyminiature bit-cells that are focus to tremendous inconsistencycorrupting their read and write-current. SRAM is a crucialfunction in varieties of purposesuch as cache memories, microprocessors and portable devices. If technology's node scaling fall, leakage power is the maintrouble in SRAM cell disturbed for the less power application. So, there is a requirement of low power adequate memory design. The futuredesign of 8x8 SRAM array is comparable to 8x8 SRAM array exploitconservative 6T SRAM cell, justsingleadditional NMOS transistor is locatedamong two cross coupled inverter. This architecture decrease static power in support mode. Cadence imitationinstrument is utilized at 90nm expertise for scheming. Relativestudy is presented in order of Leakage power consumption, Read Access time, Write Access time and Absolute Leakage power consumption. Tangentialapparatus of inclusive 8x8 SRAM array has been intendedlike SRAM cell, row /column decoder and sense amplifier.

Key Words: CMOS, SRAM, 7T SRAM Cell, Leakage Power, Cadence.

# 1. Introduction

With advancing technology, there is always an increase in demand for larger data storage capacity. It has determined the production protection and memory growth to extradense design system and to greatest data storage concentration. A variety of memories are available to store and access the information stored. Due to single requirement can choose a read only memory that areusually utilized in microcontrollers or read write memory which is normally utilized in microprocessors. In contrast with DRAM however SRAM need extra space, it is efficiently affected and group faster. DRAM dissimilar the SRAM wants to be invigorated following equivalent intermission of time. Thus for SRAMs the reserve power is extremely shortin spite of maximum density of transistors. SRAM cells have high clamor resistance because of bigger commotion edges, and have capacity to work at low power supplies. The most vital utilization of SRAM is in CPU reserve recollections, little on-chip recollections, FIFOs or different cushions. Here, we will structure 8x8 SRAM chip and examine the zone and deferral of the whole chip. The chip will contain 7 transistor SRAM cells.

Structure of 7T SRAM develop intonovelconfrontwithincapacity prerequisite in the SOC (System on Chip) at nanometer innovation in view threshold voltage disparity. Threshold voltage varieties may influence the steadiness and read/write process in the SRAM. This paperis an expansion of past structures, for example, resistive load inverter based and CMOS rationale [1]. While utilizing CMO Slogic the yield voltage swing

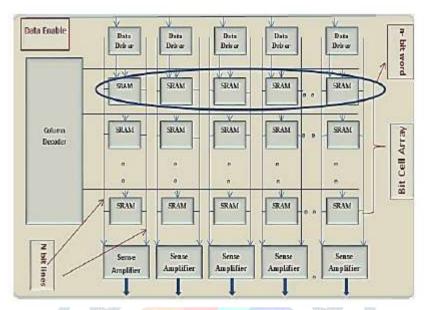

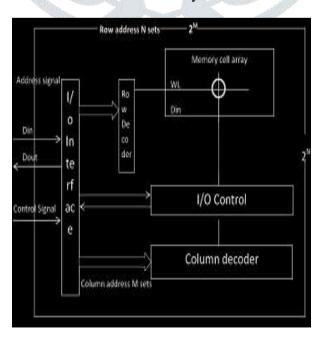

depends up on the VDD it causes extra power utilization and it takes more area because of draw up and pull down systems and utilizing extra integer of PMOS transistors the power utilization enhanced. For diminishing Leakage flows transistor scaling is the successful technique. As well as transistor scaling provide voltage scaling is notable technique to diminish thepower utilization of a circuit. The leakage is condensed owing to lesser voltage contrasts between the drain, supply and body of a transistor [2] thus, in term of paper thetotal digital blocks in the memory design are given in Fig.1.

Figure.1 Block diagram of memory architecture.

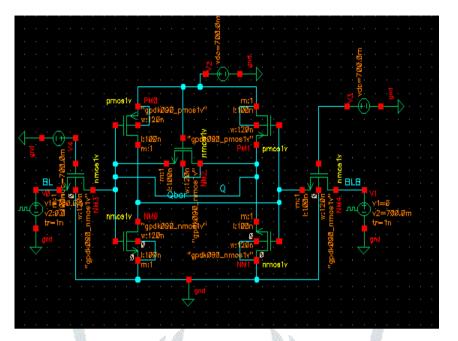

# 2. 7T SRAM Cell

Toward CMOS memory function, Memory cells are categories frequently by (1) Featured operation modes, (2) Data form, (3) Logic system, (4) Storage mode, (5) Storage operation, (6) Number of constituent elementary devices, (7) Access mode, (8) Storagemedia, (9) Radiation hardness. In this paper Memory cells are applied in array and the functions of memory cell arrays are served by all other circuit of memory [3]. In RAM, an array is arrangement of memory cells.

Write operation and read operation. This paper proposes implementation of 7T SRAM which is better in terms of Q Arrays are useful because instead of having to separately store related information in dissimilarnamed memory position. Eachfundamentalslocated to an array are roboticallyamass in adjacent memory location. The leakage current of the memory augmentby the capabilitylikeextra power will be inspiredstill in the reserve cycle. Most of system which are utilized to lessen power, thus we attempt to save power to writeand with power dissipation.

8 bit cells are used to store 8 bits at a time and produce one output at a time. Here 7T is use to store single bit. Equally BL and BLB are invigorated high prior to and subsequent to every read/write operation. Write operation is done when the center NMOS is OFF but here this NMOS is getting DT and ON, so it read at the same time and initially it generate garbage value. Balanceof data to be printed to node Q is implemented to BLB and equivalent NMOS is twisted through declaring Word line DT maximum. BL and its access

transistor do not take part in the write operation. During standby mode, both access transistors are kept off applying negative DT pulse. At the next positive pulse of DT as center NMOS is ON and read previous stored data.

Figure.2 Schematic of 7T SRAM Cell

According to read operation logic amplifier obtain BL and BLB, and read theinformationwhiledeclarationrow DT is off. 3-to-8 Decoder is used to select to write one of the all cells. In 8x8 bit array Read operation are back and forth between 8x8 bit cells. Both sense amplifier 1 and 2 produce the data of ST1 and ST2 respectively at different pulse time.

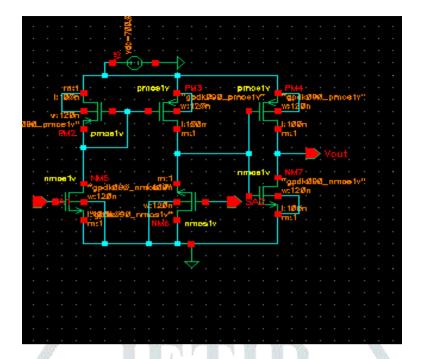

# 3. Sense Amplifier

Sense amplifiers, involvement through memory cells are mainfundamentals in determining the presentation and ecologicalacceptance of CMOS memories. We designed sense amplifier in our circuit to improve the speed performance of a memory, and to provide signals which conform to requirements of driving peripheral circuits contained by memory [4].

Sense amplifier has toexertion in the objective of circuit basics. Elementary state for logic circuit and sense amplifier operations aremainlysuitably to getsince the operation limitations of potential sense circuit. In figure 3 shown the Sense Amplifier Circuit, during read operation sense amplifier receives BL and BLB, and read the data when word line DT is off. 3-to-8 Decoder is used to select to write one of the all cells. In 8x8 bit array Read operation are back and forth between 8x8 bit cells. Both sense amplifier 1 and 2 produce the data of SA1 and SA2 respectively at different pulse time.

Figure.3 Sense Amplifier

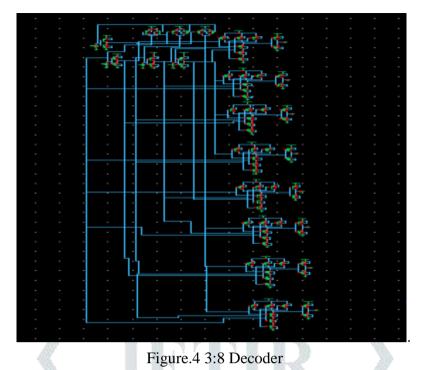

## 4. 3:8 Decoder

The 3:8decoderschoosesingle of the 2N lines as for each the address outline. The production of the decoder is supply to the remark lines in the SRAM array. Itchoose the line of SRAM collection that is access. The representation of the row decoder utilize is as given in Figure 4.

Decoder's plays an important part in SRAM design since that is the one which is going to determine the location in which we will be working among the array of memory cells arranged in a row and column fashion. Basically Row decoder is made of series of NAND gates. N i/p from the user can decode up-to 2<sup>N</sup> different rows. The column decoder also plays a vital role in selecting the exact cell in the array of cells. Column decoder is very much efficient in design no of words. Designing the column decoder is of course crucial since it sees the bit line wire length and diffusion cap of all the pass transistors connected across the word-line. It uses the concept of decoding the column address in a bit by bit fashion. Usually the final bit is the one which is going to determine the column that is to be selected. Address location first few bits will be row address and last few bits will be column address. In this paper used the 3:8 row decoder, which output connected the word line of the array.

## 5. 8x8 Memory Array Organization

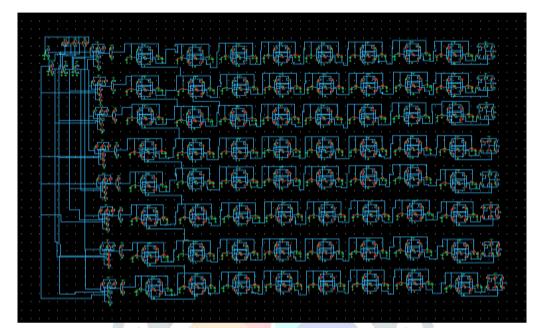

Some cell has contact at arbitraryby the identical velocity. Selecting both corresponding row and columns sometimes, the memory cell is called memory matrix, a memory array, orsimply array [5]. Therow is known as word line that are determinedmerelysinceexterior the storage collection, even as the column is known bit or data line which are dataflow into and away of cells. A cell is accessed for reading or writing by choosing its row and column. Each cell havestore 1 or 0. Memories may simultaneously select 8 cells in one row according to application [6]. A Memory cell array comprising a matrix of 8N rows and 8M columns can store binary information of 8(N+M) bits [5]. At the memory chip configuration shows figure 5, the desired logic properties are recovered through use of properly designed peripheral circuits. Those tangential circuits row, column decoder. sense amplifier, I/O control, I/O interface are etc. that isintendedaccordinglythiscancollectiveamidvarious memory cells.

## Figure.5The Memory Chip Configuration

Read/Write circuits establisheither data are individual recover or accumulate and perform suchessential amplification, buffering and transformation of voltage levels[6]. An array arrangement minimizes the no. of driving circuits of memory cells. The no. is (8N+8M), which is a minimum at N=M for matrix for 8x8 dimensional arrangement in Figure 6, while it is  $2^{(N+M)}$  for a 1 dimensional arrangement Figure.6 [7].

# 6. Simulation Results and Discussion

8x8 array using 7TSRAM Cell Simulation has been done on cadence tool using the 90nm technology with a nominal supply voltage Vdd= 0.7 V. The gate leakage being the only dominant mechanismat room temperature 27°C, Read and Write Data in to cell.

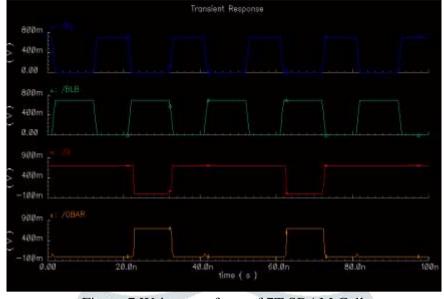

#### Writing Data in to the Cell

Different sequences of 1's and 0's were written into the memory array to make sure that the write circuitry works. Figure 7 shows the waveforms that were obtained when writing a '1' and '0' into the memory cell. As seen the when data '1' is writing, once the write signal is asserted and the word line is pulled high, the Q node starts to rise to Vdd while the Q node starts fallingalong to Gnd. The write access instance is the instance elapsed among write request and the concluding writing of the input data addicted to the memory. From simulations this was found to be 21.1ns shown in Figure7.

Figure.7 Write waveform of 7T SRAM Cell

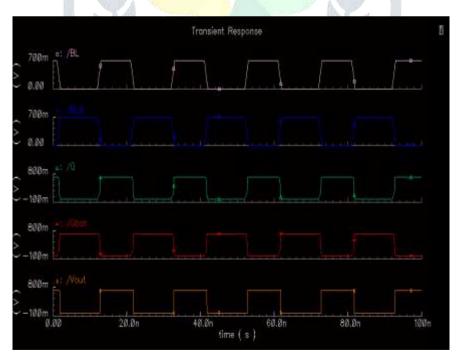

# **Reading Data from the Cell**

The data which is present in the memory array needs to be read out by the sense amplifier circuits which have to be enabled by the replica bitlinecircuit. During the read operation there are chances of the data getting destroyed. Figure 8illustrate the waveforms which was acquired from the reproduction. As seen when reading data logic '0' or logic '1' from the memory array, the voltage at node SA1 and SA2 rises up to 700mV and get output Vout. This is however not sufficient to flip the contents of the memory cell shown in Figure 8.

Figure.8 Read waveform of 7T SRAM Cell

Result Summary of8x8 Array with 7T SRAM Cellis shown below table 1.

| Table I bindiated Result buinnary |                                    |                                |

|-----------------------------------|------------------------------------|--------------------------------|

| S.no                              | Performance Parameter              | 8x8 Array with 7T SRAM<br>Cell |

| 1.                                | Supply Voltage                     | 0.7V                           |

| 2.                                | Leakage Power                      | 8.4nW                          |

| 3.                                | Total Leakage power<br>Consumption | 33.6nW                         |

| 4.                                | Read Access time                   | 21.1ns                         |

| 5.                                | Write Access time                  | 16.5ns                         |

#### **Table 1 Simulated Result Summary**

#### Conclusion

Due to this paper intend a 7T-based SRAM cell, which address the vitalcausesintended a low power SRAM in profound sub-micron expertise along byrecommended techniques utilized to conquer them. According to thiswork the presented SRAM construction are examined and next a fundamental 7T SRAM construction was selected. The 3:8decoder is implemented as a binary structure by implementing a 8-stage path. This 8x8 bit array is implemented both way and investigated separately. While designing the 8x8 Array using 7T-based SRAM cell to minimize the LeakagePower, working Low Power and improve the Read and Write access time.Thefuture architecture of 8x8 SRAM collections is comparable to 8x8 SRAM collection utilizeconservative 6T SRAM cell, solitaryextra NMOS transistor is locatedamong two cross coupled inverter. This design lessens static power in reserve mode. Cadence simulation tool is utilized at 90nm expertise for scheming. The proportionalstudy is achieved in conditions of Leakage power consumption, Read, Write Access time and entire leakage power consumption.

#### References

- 1. R. Bisht, P. Aggarwal, P. Karki and P. Pande. 2016. Low power and noise resistant 16×16 SRAM array design using CMOS logic and differential sense amplifier. 2016 International Conference on Computing, Communication and Automation (ICCCA), Noida. pp. 1474-1478.

- D. Ho, K. Iniewski, S. Kasnavi, A. Ivanov and S. Natarajan. 2006. Ultra-low power 90nm 6T SRAM cell for wireless sensor network applications. 2006 IEEE International Symposium on Circuits and Systems, Island of Kos. p. 4, doi: 10.1109/ISCAS.2006.169353.

- 3. T. P.Haraszti (microcircuit associates)," CMOS Memory Circuits" by Kluwer Academic publisher, second printing with correctness 2001 Boston / Dordecht / London, ",copyright 2000.

- Chotaro Masuda, Tetsuya Hirose, Kei Matsumoto, Yuji Osaki, Nobutaka Kuroki, and Masahiro Numa, "High Current Efficiency Sense Amplifier Using Body-Bias Control for Ultra-Low-Voltage SRAM", in Circuits and Systems (MWSCAS), 2011 IEEE 54th International Midwest Symposium,2011.

- 5. K. Itoh, "VLSI Memory Chip Design" copyright, verlag Berlin Heidelberg, 2001 Springer

- HirdayaNarain Mishra, and Yashwanta Kumar Patel "Design, Simulation and Characterization of Memory Cell Array for Low Power SRAM using 90nm CMOS Technology"IEEE International Conference on Power, Control and Embedded Systems(ICPCES) January 2011, pp. 1-3.

- 7. M. Morris Mano, professor of Engineering, California State University, Los Angeles, "Digital Logic and Computer Design" Published by Dorling Kindersley (India) Pvt. Ltd., licensees of Pearson Education inSouth Asia.