# FOLDED ARCHITECTURE BASED CARRYSKIP ADDER FOR M BIT

P.Murali Babu<sup>1</sup>, R.Trinadh<sup>2</sup>

<sup>1</sup>PG Scholar, Electronics and Communication Engineering, Sir C R Reddy College of Engineering, AP, India <sup>2</sup>Assistant Professor, Electronics and Communication Engineering, Sir C R Reddy College of Engineering, AP, India

Abstract: In computerized PCs fundamental tasks, for example, option and subtraction, duplication is executed utilizing continued including and division by rehashed subtraction which can be modified. Adders are utilized in ALUs (math rationale units), as well as in numerous circuits utilized in of the processors including computerized flag processors and broadly useful processors. So enhancing rate and vitality parameters of adders will enhance the execution of entire ALU. Diverse kinds of adders are accessible in the market, for example, swell convey viper, convey look forward snake, convey select viper, Carry skip viper and so forth. In this proposition, distinctive Carry skip adders are analyzed and somewhat adjusted form in engineering is recommended that can expand the speed. It consolidates a convey feed forward square to the current structures with the goal that the postponement can be diminished. The proposed design can be utilized for rapid application by the expense of Speed. The adders looked at in this theory are CSKA (ordinary convey skip viper) and CI-CSKA (Concatenation Incrementation Carry skip snake), and the proposed models are CFF-CSKA (Carry Feed Forward CSKA) and CFF-CI-CSKA. Collapsed Architecture is a procedure of consolidating the N number of units into a solitary unit for the most part in our specific procedure we are valuably decreasing the measure of 8 bit design and upgrading the restrictions of individual cell from these we diminishing the span of chip. Hence, unit gets the convey skip inspirations tunes to our outcomes. In this procedure delay get decreased by 25% of (Latency utilized already) Existed Scheme.

### Keywords: ALUs, speed, carry feed forward, CI-CSKA, CFF-CSKA, CFF-CI-CSKA.

#### I. INTRODUCTION

ADDERS are a key building obstruct in number juggling and rationale units (ALUs) [1] and subsequently expanding their speed and lessening their capacity/vitality utilization emphatically influence the speed and power utilization of processors. There are numerous deals with the subject of streamlining the speed and intensity of these units, which have been accounted for in [2]– [9]. Clearly, it is exceedingly alluring to accomplish higher velocities at lowcontrol/vitality utilizations, which is a test for the creators of universally useful processors. Low power number juggling circuits have turned out to be imperative in VLSI industry. Because of the quick development of convenient electronic part, Adder circuit is the fundamental building obstruct in DSP processor.

Viper is the fundamental part of number juggling unit. A Complex DSP framework includes a few adders. The Designers are constrained with more imperatives are fast, high throughput, little silicon zone and low power utilization. Many plan styles of adders exist. Despite the fact that, Ripple convey adders are the little in configuration structure yet its slower. Most as of late, convey skip adders [1, 2, 3] are utilized famously because of their execution of fast and little size. For the most part, in a N-bit convey skip snake separated into M-bit number of squares [1, 4], a longscope of convey flag begins at a square Bi, which undulating through a few bits in that square, at that point it skirts a few squares, and closures with a square Bj. Convey look-ahead and convey select adders are quick yet far bigger and devour substantially more power than swell or convey skip adders.

Two of the quickest realized expansion circuits are the Lynch-Swartzlander's [5] and Kantabutra's [6]hybrid convey

look-ahead adders. They depend on the utilization of a convey tree that produces conveys into suitable piece positions without back proliferation. With the end goal to get the legitimate whole bits at the earliest opportunity, in both Lynch-Swartzlander's and Kantabutra's adders the aggregate bits are figured by methods for convey select squares, which can play out their activities in parallel with the convey tree Recently, the close edge district has been considered as an area that gives a more attractive tradeoff point among deferral and power scattering contrasted and that of the subthreshold one, since it results in lower delay contrasted and the subthreshold locale and altogether brings down exchanging and spillage powers contrasted and the superthreshold area.

Furthermore, close limit task, which utilizes supply voltage levels close to the edge voltage of transistors [11], experiences extensively less the procedure and natural varieties contrasted and the subthreshold district. The reliance of the power (and execution) on the supply voltage has been the inspiration for plan of circuits with the component of dynamic voltage and recurrence scaling. In these circuits, to lessen the vitality utilization, the framework may change the voltage (and recurrence) of the circuit dependent on the outstanding task at hand prerequisite [12]. For these frameworks, the circuit ought to have the capacity to work under an extensive variety of supply voltage levels.

#### **II FOLDED ARCHITECTURE**

Collapsed engineering in Carry Skip Adder we can accomplish Time - Power Consumption. Execution and cost of any computerized Circuit relies upon circuit configuration style. In Parallel Optimization will be Reduce the clock time frame, decreasing the quantity of registers, diminishing the Power Consumption, A possibility of lessening the Latency of the circuit. This postulation centers around engineering structures and advancement strategy, called collapsing, which allotments applications into an arrangement of stages to transiently have a similar equipment/programming assets. The zone utilization is altogether lessened, which additionally enhances the interconnect execution and power utilization. Next, seeing that rationale collapsing diminishes region altogether and the greater part of interconnects are limited, the proposition proposes explicitly advanced for rationale collapsing. It kills the vast majority of the worldwide interconnect assets, which possess an expansive portion of territory in customary equipment/Software. As the Area is decreased by presenting the collapsed design utilization of less silicon should be possible and furthermore demonstrates the effect in the aggregate size of the hardware.

Power Consumption is lessened because of the expelling of extra hardware and speed of the circuits additionally expanded. Obviously, accomplishing higher paces at lower supply voltages for the computational squares, with the viper as one the principle parts, could be essential in the structure of rapid, yet vitality effective, processors. In this paper, given the appealing highlights of the CSKA structure, we have concentrated on lessening its postponement by adjusting its execution dependent on the static CMOS rationale. The focus on the static CMOS starts from the longing to have a dependably working circuit under an extensive variety of supply voltages in profoundly scaled innovations [10]. The proposed alteration builds the speed extensively while keeping up the low zone and power utilization highlights of the CSKA. Likewise, an alteration of the structure, in view of the variable idleness method, which thus brings down the power utilization without significantly affecting the CSKA speed, is additionally

#### Improving Efficiency of Adders at Low Supply Voltages

To improve the performance of the adder structures at low supply voltage levels, some methods have been proposed in . In adaptive clock stretching operation has been suggested. The method is based on the observation that the critical paths in adder units are rarely activated. Therefore, the slack time between the critical paths and the off-critical paths may be used to reduce the supply

voltage. Notice that the voltage reduction must not increase the delays of the noncritical timing paths to become larger than the period of the clock allowing us to keep the original clock frequency at a reduced supply voltage level. When the critical timing paths in the snake are actuated, the structure utilizes two clock cycles to finish the task. Along these lines the power utilization lessens impressively at the expense of rather little throughput debasement. In the proficiency of this strategy for lessening the power utilization of the RCA structure has been illustrated. The CSLA structure in [28] was upgraded to utilize versatile clock extending activity where the improved structure was called course CSLA (C2SLA). Contrasted and the normal CSLA structure, C2SLA utilizes increasingly and diverse sizes of RCA squares. Since the slack time between the basic planning ways and the longest off-basic way was little, the supply voltage scaling, and thus, the power decrease were restricted. At long last, utilizing the half and half structure to enhance the viability of the versatile clock extending task

introduced. To the best of our insight, no work focusing on plan of CSKAs working from the superthreshold area down to close edge district and furthermore, the plan of (cross breed) variable inertness CSKA structures have been accounted for in the writing.

### **III. PRIOR WORK**

#### Modifying CSKAs for Improving Speed

Alioto and Palumbo [19] propose a basic procedure for the plan of a solitary dimension CSKA. The strategy depends on the VSS system where the close ideal quantities of the FAs are resolved dependent on the skip time (postponement of the multiplexer), and the swell time (the time required by a help to swell through a FA). The objective of this strategy is to diminish the basic way delay by considering a noninteger proportion of the skip time to the swell time on in opposition to a large portion of the past works, which considered a whole number proportion [17], [20]. In the majority of the works evaluated up until this point, the emphasis was on the speed, while the power utilization and zone use of the CSKAs were not considered. Notwithstanding for the speed, the postponement of skip rationales, which depend on multiplexers and shape a vast piece of the snake basic way delay [19], has not been diminished.

has been examined In the proposed mixture structure, the KSA has been utilized in the center piece of the C2SLA where this blend prompts the positive slack time increment. In any case, the C2SLA and its half and half form are bad contender for low-control ALUs. This announcement starts from the way that because of the rationale duplication in this kind of adders, the power utilization and furthermore the PDP are still high even at low supply voltages The CSKA might be actualized utilizing FSS and VSS where the most noteworthy speed might be gotten for the VSS structure Here, the stage estimate is equivalent to the RCA square size. In Sections III-An and III-B, these two unique executions of the CSKA snake are depicted in more detail. The structure depends on joining the connection and the incrementation plans [13] with the Conv-CSKA structure, and consequently, is signified by CI-CSKA. It gives us the capacity to utilize less difficult convey skip rationales. The rationale replaces 2:1 multiplexers by AOI/OAI compound entryways (Fig. 2). The entryways, which comprise of less transistors, have bring down postponement, zone, and littler power utilization contrasted and those of the 2:1 multiplexer [37]. Note that, in this structure, as the help proliferates through the skip rationales, it moves toward becoming supplemented. In this manner, at the yield of the skip rationale of even stages, the supplement of the convey is produced. The structure has a significant lower engendering delay with a marginally littler zone contrasted and those of the customary one. Note that while the power utilizations of the AOI (or OAI) entryway are littler than that of the multiplexer, the power utilization of the proposed CI-CSKA is somewhat more than that of the traditional one. This is because of the expansion in the quantity of the doors, which forces a higher wiring capacitance (in the noncritical ways). The explanation behind utilizing both AOI and OAI compound entryways as the skip rationales is the reversing elements of these doors in standard cell libraries. Along these lines the requirement for an inverter door, which expands the power utilization and postponement, is wiped out. As appeared in Fig. 2, if an AOI is utilized as the skip rationale, the following skip rationale should utilize OAI door. What's more, another point to make reference to is that the utilization of the proposed skipping structure in the Conv-CSKA structure expands the deferral of the basic way significantly. This begins from the way that, in the Conv-CSKA, the skip rationale (AOI or OAI compound entryways) can't sidestep the zero convey contribution until the point when the zero convey input engenders from the comparing RCA square.

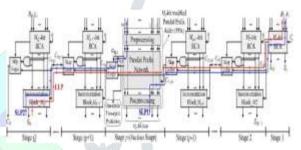

#### **IV PROPOSED CSKA STRUCTURE**

The proposed CFF-C.I.CSKA utilizes the equivalent CFF component which is utilized by CFF-CSKA. That is to produce the convey from of the information bits. The information bits are first sustained to a XOR entryway. The yield of this XOR entryway is nourished to AND-OR rationale to create the convey of each RCA square. The square which is utilized to produce convey is convey feed forward square and the entire proposed design is appeared in Fig.4.2. The convey created by this convey feed forward square is encouraged to the second entryway of AOI-OAI skip rationale. In situations where the info bits are not in engendering mode the CFF square will create the convey yield utilizing ANDOR rationale, from the XOR ed input bits. The CFF square requires two three info AND entryway and one OR door. Since the convey gave to each RCA square is zero, the quantity of AND doors in convey feed forward square can be constrained to three. Since the last full snake is adjusted without AND doors, the recently included square requires just a single and one OR entryway. By including 4-XOR doors, one and one OR entryway for each square it is conceivable to make the C.I.CSKA to skip convey in all conditions.Since the convey contribution to each RCA square is zero, the main full viper in each RCA square can be supplanted considerably adders. Likewise the convey produced by RCA square isn't required on the grounds that the convey feed forward square creates the convey. Subsequently the last full viper of RCA chain is adjusted so that the two AND entryways required for the age of yield convey is evacuated. The convey created by CFF square helps the second door in the AOI-OAI rationale to choose the convey of next square. The preferred standpoint is that if the bits are not in proliferation mode the snake should hold up until the convey of RCA square is created. This design has such a significant number of points of interest.Each 4-bit CSA block is formed by falling four FAs. As the mirror circuit just delivers Co. Along these lines, on the off chance that we need to interface two FAs, we have to alter it back to Co. Nonetheless, this can back off the entire circuit since it will add more inverters to the convey spread way. Luckily, on the off chance that we transform every one of the A, B and Ci signals, from the conditions (1, 2, 3), estimation of P does not change while estimations of both S and Co are rearranged. From this

perception, the 4-bit CSA square can be shaped as portrayed, no inverter is required at the convey yields of every FA. The convey is skipped if  $P_{-} = P3P2P1P0 = 1$  (as appeared in Fig. 1). To keep away from a high fan-in circuit that can make the Ion/Io f proportion low at sub limit voltages, the rationale P is shaped from just 2-input NAND and NOR entryways (rather than a 4-info AND doors). The 2-input NAND and NOR entryways with transistor estimating all together that they have most pessimistic scenario pull-up and pull-down occasions equal to a base size adjusted inverter (which was appeared in Fig. 1.10). The complete of a 4-bit CSA square is gotten from a 2-input MUX. This MUX utilizes a transmission door with support (by an inverter) at yield as appeared in Fig. 6. Advantage of the yield cushion here is two-overlap. To start with, it makes Cout more grounded at yield of every 4-bit CSA square. Second, it maintains a strategic distance from the situation when C0 can be skipped and goes through each of the eight 4-bit hinders with no middle support. This will genuinely debase the last convey yield motion because of powerless driving current (so it won't meet the strength necessity of VOL \_ 0.1VDD and VOH \_ 0.9VDD even at high supply voltages), and furthermore backs off the general speed of the snake.

#### V RESULTS

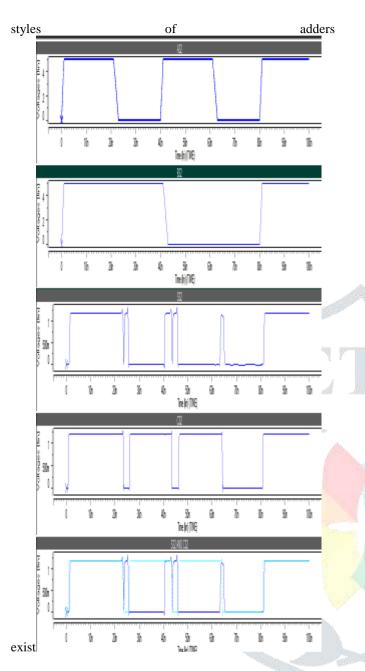

The structure proposed in this paper has been created utilizing MODEL SIMULATOR. ADDERS are a key building obstruct in number juggling and rationale units (ALUs). Low power number juggling circuits have turned out to be critical in VLSI industry. Snake circuit is the fundamental building obstruct in DSP processor. Snake is the fundamental part of number juggling unit. A complex DSP framework includes a few adders. Many structure

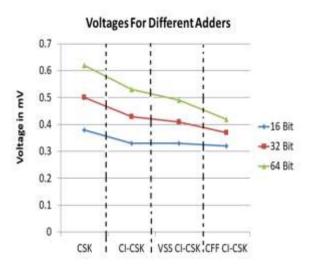

## Comparison of delay, Energy/Power Consumption and Voltages 16bit, 32bit and 64bit is as follows:

The Observed power calculations was done and plotted with nominal VDD=1.1V and we can clearly observe the comparison of previous structures with the proposed scheme 32-Bit 16-Bit & 64-Bit.

Table 6.1: Changes of delay, power and voltage for the proposed CFF CI-CSK Structure compared with other structures in the case of 16 Bit length.

| 16 bit                    | CSK  | CI-<br>CSK | VSS<br>CI-<br>CSK | CFF<br>CI-<br>CSK |

|---------------------------|------|------------|-------------------|-------------------|

| Delay (nS)                | 4.56 | 4.5        | 4.45              | 4.36              |

| Operating Voltage<br>(mV) | 0.38 | 0.33       | 0.33              | 0.32              |

| Power<br>Consumption(uW)  | 6.23 | 8.1        | 8.27              | 7.95              |

Table 6.2: Changes of delay, power and voltage for the proposed CFF CI-CSK Structure compared with other structures in the case of 32 Bit length.

| 32 bit                    | CSK  | CI-<br>CSK | VSS<br>CI-<br>CSK | CFF<br>CI-<br>CSK |

|---------------------------|------|------------|-------------------|-------------------|

| Delay (nS)                | 4.68 | 4.6        | 4.53              | 4.41              |

| Operating Voltage<br>(mV) | 0.5  | 0.43       | 0.41              | 0.37              |

| Power<br>Consumption(uW)  | 6.35 | 8.20       | 8.35              | 8.00              |

Table 6.3: Changes of delay, power and voltage for the proposed CFF CI-CSK Structure compared with other structures in the case of 32 Bit length.

| 64 bit                    | CSK  | CI-<br>CSK | VSS<br>CI-<br>CSK | CFF<br>CI-<br>CSK |

|---------------------------|------|------------|-------------------|-------------------|

| Delay (nS)                | 4.8  | 4.7        | 4.61              | 4.46              |

| Operating Voltage<br>(mV) | 0.62 | 0.53       | 0.49              | 0.42              |

| Power<br>Consumption(uW)  | 6.47 | 8.3        | 8.43              | 8.05              |

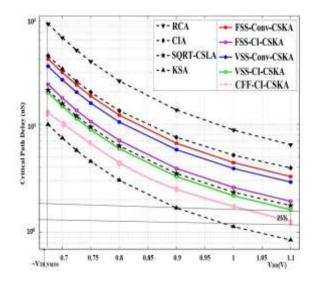

Fig4.4: Critical Path Delay vs VDD Graphical Representation

As shown in above graph we can see the difference between the existing and proposed scheme. Having the overall path delay reduce up to 25%. That Nominal Voltage=1.1V. the delay get reduce at the  $32_{th}$ stage.

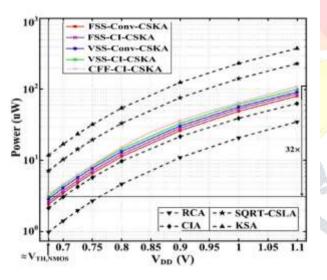

# The Following graphical representation was the POWER and VDD as follows:

The following Graphical representation was the Operating Voltage for various schemes and Proposed Scheme with 16-Bit,32-Bit,64-Bit,

Fig 4.6: Graphical Representation of Voltage (Nominal Voltage=1.1V) for the proposed CFF CI-CSK Structure compared with previous structures in the case of 16, 32 & 64 Bit length.

Operating Voltage was the point where the output get operated it mean starting point from the raising time of the signal.

The Power Consumptions of adders vs the supply voltages are shown in above representations. The results reveal that the smallest power consumption belongs to the RCA, while KSA structure consumes the highest power owing to its parallel structure. As observed reference figure and graphical representations our Proposed structure reduce the delays further such that in the case of VSS, the delay even becomes even lower. The delay reductions of the CFF CI-CSK compared with those of

CSK were in the range of 12%-11%.

CI-CSK were in the range of 10%-9%.

VSS CI-CSK were in the range of 8%-6%.

CFF-CI-CSK were in the range of 5%.

At long last, the outcomes demonstrated that the diminishing the postponement and working voltage likewise get lessened. 1.1V was the nMoS ostensible edge Voltage. The 8-bit was hypothetically determined as 8x4.41nS=35~32(Sec) of deferral for the snake.

#### VI. CONCLUSION

In this paper, a static CMOS CSKA structure called CI-CSKA was proposed, which shows a higher speed and lower vitality utilization contrasted and those of the regular one. The speed improvement was accomplished by adjusting the structure through the link and incrementation procedures. Also, AOI and OAI compound doors were misused for the convey skip rationales. The effectiveness of the proposed structure for both FSS and VSS was considered by contrasting its capacity and delay and those of the Conv-CSKA, RCA, CIA, SQRT-CSLA, and KSA structures. The outcomes uncovered impressively bring down PDP for the VSS usage of the CI-CSKA structure over an extensive variety of voltage from super-limit to close edge. The outcomes likewise recommended the CI-CSKA structure as a decent viper for the applications where both the speed and vitality utilization are basic. Moreover, a half and half factor inactivity expansion of the structure was proposed. It abused an adjusted parallel snake structure at the center stage for expanding the slack time, which furnished us with the open door for bringing down the vitality utilization by decreasing the supply voltage. The viability of this structure was looked at versus those of the variable inertness RCA, C2SLA, and half breed C2SLA structures. Once more, the proposed structure demonstrated the most reduced deferral and PDP improving itself as a possibility for fast low-vitality applications. **REFERENCES**

[1] Milad Bahadori, Mehdi Kamal, Ali Afzali-Kusha,"

High-Speed and Energy-Efficient Carry Skip Adder

Operating Under a Wide Range of Supply Voltage Levels"

IEEE Transactions on Very Large Scale Integrations (VLSI)

Systems, VOL.24, NO. 2, Feb 2016.

[2] S.V.Manikanthan and T.Padmapriya "Recent Trends In M2m Communications In 4g Networks And Evolution Towards 5g", International Journal of Pure and Applied Mathematics, ISSN NO: 1314-3395, Vol-115, Issue -8, Sep 2017.

[3] S.V.Manikanthan and V.Rama "Optimal Performance Of Key Predistribution Protocol In Wireless Sensor Networks" International Innovative Research Journal of Engineering and Technology ,ISSN NO: 2456-1983,Vol-2,Issue –Special –March 2017.

[4] S.V.Manikanthan, Padmapriya.T, "RECENT TRENDS IN M2M COMMUNICATIONS IN 4G NETWORKS AND EVOLUTION TOWARDS 5G", International Journal of Pure and Applied Mathematics, Vol. 115, No. 8, pp: 623-630, 2017.

[5] Ragunath, G., Sakthivel, R. Low - power and area efficient square - Root carry select adders using modified XOR gate (2016) Indian Journal of Science and Technology.

[6] Rajesh.M., and J. M. Gnanasekar. & quot; GC Cover Heterogeneous Wireless Ad hoc Networks.& quot; Journal of Chemical and Pharmaceutical Sciences (2015): 195-200.

[7] Kerur, S.S., Saktivel, R., Kittur, H., Girish, V.A Low power high performance carry select adder (2014) International Journal of Applied Engineering Research, 9 (2), pp. 175-182.

[8] R. Zlatanovici, S. Kao, and B. Nikolic, "Energy– delay optimization of 64-bit carry-lookahead adders with a 240 ps 90 nm CMOS design example," IEEE J. Solid- State Circuits, vol. 44, no. 2, pp. 569–583, Feb. 2009.

[9] S. K. Mathew, M. A. Anders, B. Bloechel, T. Nguyen, R. K. Krishnamurthy, and S. Borkar, "A 4-GHz 300-mW 64-bit integer execution ALU with dual supply voltages in 90-nm CMOS,"IEEE J. Solid-State Circuits, vol. 40, no. 1, pp. 44–51, Jan. 2005.

[10] V. G. Oklobdzija, B. R. Zeydel, H. Q. Dao, S. Mathew, and R. Krishnamurthy, "Comparison of high performance VLSI adders in the energy-delay space," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 13, no. 6, pp. 754– 758, Jun. 2005.

[11] M. Alioto and G. Palumbo, "A simple strategy for optimized design of one-level carry-skip adders," IEEE

Trans. Circuits Syst. I, Fundam. Theory Appl., vol. 50, no. 1, pp. 141–148, Jan. 2003.

[12] P. M. Kogge and H. S. Stone, "A parallel algorithm for the efficient solution of a general class of recurrence equations," IEEE Trans. Comput., vol. C-22, no. 8, pp. 786–793, Aug. 1973.

[13] M. Lehman and N. Burla, "Skip techniques for high-speed carry propagation in binary arithmetic units," IRE Trans. Electron. Comput. vol. EC-10, no. 4, pp. 691–698, Dec. 1961.

[14] I. Koren, *Computer Arithmetic Algorithms*, 2nd ed. Natick, MA, USA: A K Peters, Ltd., 2002.

[15] R. Zlatanovici, S. Kao, and B. Nikolic, "Energy–delay optimization of 64-bit carry-lookahead adders with a 240 ps 90 nm CMOS design example," *IEEE J. Solid-State Circuits*, vol. 44, no. 2, pp. 569–583, Feb. 2009.

[16] S. K. Mathew, M. A. Anders, B. Bloechel, T. Nguyen, R. K. Krishnamurthy, and S. Borkar, "A 4-GHz 300-mW 64-bit integer execution ALU with dual supply voltages in 90-nm CMOS,"

*IEEE J. Solid-State Circuits*, vol. 40, no. 1, pp. 44–51, Jan. 2005.

[17] V. G. Oklobdzija, B. R. Zeydel, H. Q. Dao, S. Mathew, and R. Krishnamurthy, "Comparison of high-performance VLSI adders in the energy-delay space," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 13, no. 6, pp. 754– 758, Jun. 2005.

[18] B. Ramkumar and H. M. Kittur, "Low-power and areaefficient carry select adder," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 20, no. 2, pp. 371–375, Feb. 2012.

[19] M. Vratonjic, B. R. Zeydel, and V. G. Oklobdzija,

"Low- and ultra low-power arithmetic units: Design and comparison," in *Proc. IEEE Int. Conf. Comput. Design, VLSI Comput. Process. (ICCD)*, Oct. 2005, pp. 249–252. [20] C. Nagendra, M. J. Irwin, and R. M. Owens, "Areatime-power tradeoffs in parallel adders," *IEEE Trans. Circuits Syst. II, Analog Digit. Signal Process.*, vol. 43, no. 10, pp. 689–702, Oct. 1996.

[21] Y. He and C.-H. Chang, "A power-delay efficient hybrid carrylookahead/ carry-select based redundant binary to two's complement converter," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 55, no. 1, pp. 336–346, Feb. 2008.