# IMPLEMENTATION OF 64-BIT MAC UNIT USING VEDIC MATHS AND REVERSIBLE LOGIC GATES

Mr. Mohan kumar D<sup>1</sup>, Ms.Harshitha K<sup>2</sup>, Harsha kumar H S<sup>3</sup> Dept. of Electronics and Communication, VFSTRU, Guntur, India<sup>1</sup> Dept. of Electronics and Communication, Mycem College, Mysore, India<sup>2</sup> Dept. of Computer Engineering, Mycem College, Mysore, India<sup>3</sup>

*Abstract:* In this paper 64 bit Multiply and Accumulate Unit (MAC) is implemented by using Vedic Multiplier and Reversible Logic Gates. A Vedic multiplier is composed by utilizing the algorithm called Urdhava Triyagbhayam sutra. The reversible logic gates are used to design the adder and they are major prerequisite for the developing field of Quantum processing. The more performance and lesser silicon area are obtained by using the Vedic multiplier by reducing the partial products .The less power is obtained by using the reversible logic. The HDL-Verilog code is used for the MAC design. The simulation and synthesis is done in Xilinx 14.1 ISE design suite.

## IndexTerms - Urdhwa Tiryabhyam Sutra, Kogge Stone Adder, Vedic Multiplier, MAC unit.

#### 1. INTRODUCTION

The Multiply and Accumulate unit is a hardware unit that performs the basic arithmetic operations like addition, subtraction and also calculus operations. The Mac takes the multiplier and multiplicand as its input and it consists of three blocks. The Mac output and one adder input will join and it forms the multiplication unit, another input of the adder, multiplier unit are joined by accumulate register. Microprocessor, Logic unit and DSP are main applications of the MAC unit. The designs obtained by MAC are non linear in nature they are discrete cosine or FFT. The entire speed of addition operation and multiplication operation of the system decides performance and whole speed. Long multiplication process creates critical delay and propagation delay exhibits to the parallel addition in the adder. The multiplier is more significant and its operation is very fast for this reason multipliers plays very important role in designing of the digital processors.

# 2. MAC ARCHITECTURE

MAC unit is a hardware unit that performs computation of two numbers and its operation is represented as follows

$X \leftarrow X + (Y^*Z) \dots \dots \dots (1)$

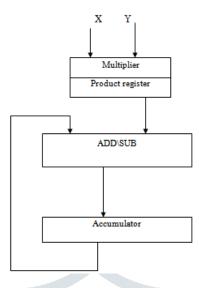

MAC unit calculates the product of 2 binary numbers and join that result to an accumulator unit. It consists of three blocks namely multiplier, adder and accumulator as shown in the figure 1. Combinational logics are used to implement the multiplier and adder is followed by the multiplier which is used to add or join the 2 binary numbers and finally stores the result in accumulator stage. For each clock pulse the output of accumulator is fed to the adder input at that time output of the multiplier is added to the accumulator stage. More number of logic are required for combinational multiplier but it calculates the product very rapidly compare to shifting and adding method. Digital signal processors are the first processors which are planned by Mac units.

#### 2.1 vedic multiplier-urdhwa tiryabhyam sutra

This algorithm is otherwise called vertical and transversely algorithm. In this algorithm partial products computation takes only one step hence it doesn't require the shift operation .The important goal of this algorithm is save time and total power. This technique is time, region and force efficient. The Urdhva-Tiryakbyham algorithm is used for the larger multiplication operations; it offers better performance contrast to further algorithms.

# Generalized Algorithm for Urdhva-Tiryakbyham sutra

Let us take two N binary bit numbers A and B are inputs where  $n=1, 2, 3 \dots N$ . where A =a  $a_{n,\dots,n}a_{1,a_{2}}, a_{3}$  and B =  $b_{n,\dots,n}b_{1,b_{2,b_{3}}}$ . The output is represented as S of (n+n) bits where  $S = s_{(n+n),\dots,n}s_{1,s_{2,s_{3}}}$ . The algorithm consists of three steps are given below.

Fig 1: Design of MAC unit

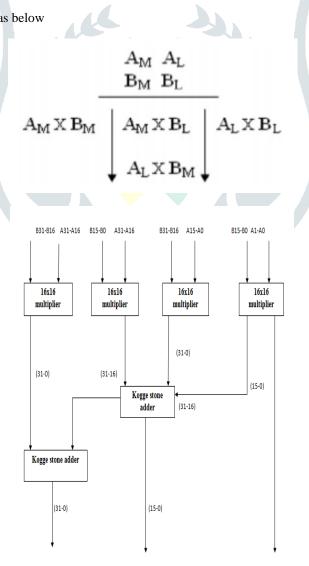

**Step 1**: The multiplicand A and multiplier B divide into 2 equal parts. One part is represented as [N to N/2+1] bit and another is represented as [N/2 t0 1] bit respectively. First bit points MSB and last bit points LSB.

Step 2: A is written as  $A_M$  and  $A_L$ . B is written as  $B_M$  and  $B_L$ .

Step 3: The general format is given as below

Fig 2:32\*32 MAC unit with Kogge stone adder

## **3. KOGGE STONE ADDER**

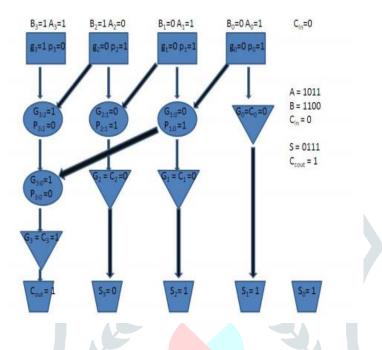

KSA is a collateral prefix invert adder and it's one of the speediest adders hence it's widely used in industry. The Kogge stone has minimum argumentation depth, maximum fork count, and negligible fan out. While a high fork number infers a bigger zone, the low rationale profundity and negligible fan-out permit quicker execution. KSA consists of three different parts as shown in the below fig3.

Fig 3: Different working blocks of Kogge stone adder

## 4. RESULTS

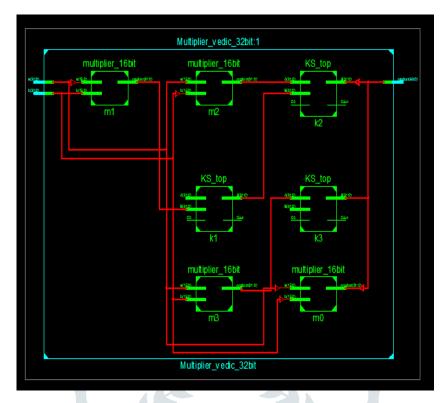

In this section implemented result for MAC unit using Kogge stone adder and multiplier is displayed in fig 4 and RTL view of the MAC unit is displayed in fig5.

| 🛪 File Edit View Simulation Window Layout Help        |                                               |             |               |                  |        |              |              |              |              |

|-------------------------------------------------------|-----------------------------------------------|-------------|---------------|------------------|--------|--------------|--------------|--------------|--------------|

| 🗋 ờ 🖥 😓 🐇 🛍 🗅 🗙 🔇                                     | N CH 🕅 🕅                                      | 1 1 🛛 🖻 🗄 🖯 | •             | <i>₽</i> k?      | ء 🕫    | 🖉 🏓 🗟 🗠      | ±   †  ≏ ^i  |              | 00us 💌 🔙     |

| Instances and Processes ↔ □ ♂ ×                       | Objects                                       | ⇔□₽×        | Ð             |                  |        |              | 1,187,881 ps |              |              |

|                                                       | Simulation Objects for Multiplier_vedic_32bit |             | ۶             |                  |        |              |              |              |              |

|                                                       | HUHUUU 😫                                      |             |               | Name             | Value  | 1,187,880 ps | 1,187,881 ps | 1,187,882 ps | 1,187,883 ps |

| Instance and Process Name D                           |                                               |             | 8             | 🕨 🖬 a[31:        | 122    |              | 122          |              |              |

| Multiplier_vedic_32bit M                              | bject Name                                    | Value 🗖     | , –           | ▶ 📑 b[31:        | 122    |              | 122          |              |              |

| ⊳ 📒 gibi gi                                           | product[63:0]                                 | 4295113252  |               | 🗓 cin            | 1      |              |              |              |              |

|                                                       | 📷 mul2[31:0]                                  | 0           | _             |                  | 429511 |              | 4295113      | 52           |              |

|                                                       | mul3[31:0]                                    | 0           | $\Theta$      | · · · ·          |        |              |              | 52           |              |

|                                                       | 💑 mul4[31:0]                                  | 0           | , t <b>*</b>  | 🕨 📑 a1[31        |        |              | 1            |              |              |

|                                                       | a1[31:0]                                      | 1           | <b>d</b> r    | 🕨 😽 a2[31        | 2      |              | 2            |              |              |

|                                                       | a3[31:0]                                      | 1 2         | -             | 🕨 📑 a3[31        | 1      |              | 1            |              |              |

|                                                       | a2[31:0]                                      | 122         | ł             | 🕨 📑 muli         | 14884  |              | 14884        |              |              |

|                                                       | mul1[31:0]                                    | 14884       | r h           | 🕨 📑 mul2         | 0      |              | 0            |              |              |

|                                                       | b[31:0]                                       | 122         | $\rightarrow$ | 📕 📑 mul3         | 0      |              | 0            |              |              |

|                                                       | la d                                          | 0           | 101           |                  |        |              | 0            |              |              |

|                                                       | 16 (2                                         | 0           | 5             | ▶ 📑 mul4         |        |              | 0            |              |              |

|                                                       | Цa                                            | 0           | XI            | Ц сі             | 0      |              |              |              |              |

|                                                       | 🖞 cin                                         | 1           |               | Ц_ с2            | 0      |              |              |              |              |

|                                                       |                                               |             |               | Ц в              | 0      |              |              |              |              |

|                                                       |                                               |             |               |                  |        |              |              |              |              |

|                                                       |                                               |             |               |                  |        |              |              |              |              |

|                                                       |                                               |             |               |                  |        |              |              |              |              |

|                                                       |                                               |             |               | X1: 1,187,881 ps |        |              |              |              |              |

| < >                                                   |                                               |             |               |                  |        |              |              |              |              |

|                                                       |                                               |             |               |                  |        |              |              |              | P            |

| 🔓 Instanc 📴 Memory 📔 Source 🕢 III 🕨 🕨 Default.wcfg* 区 |                                               |             |               |                  |        |              |              |              |              |

Fig 4: Simulation results of 32\*32 MAC Unit

Fig 5: MAC with Kogge stone adder RTL view

# **5. CONCLUSION**

From this project we can conclude that the outcome obtained by Vedic multiplier with 64 bit and reversible barrier is very great. The work exhibited depends on 64 bit MAC unit with multipliers.MAC is a essential building for multiplication operations and its amalgation for all units, hence Uradhya-Tiryakbhayam with 64 bit invert rationale and multiply and accumulate unit is best in all views are velocity, zone, many sided quality.MAC unit is basic basement for different designs and other perspectives. Consolidating the Vedic maths and reversible rationale will prompt new and proficient accomplishments in creating different fields of Mathematics and science.

## REFERENCES

[1] R. Anitha, Sarat Kumar Sahoo and Jacob Reglend. I, "A 32 BIT MAC Unit Design Using Vedic Multiplier and Reversible Logic Gate" 2015 International Conference on Circuit, Power and Computing Technologies [ICCPCT], 2015 IEEE.

[2] Manoranjan Pradhan, Rutuparna Panda and Sushanta Kumar Sahu "Speed Comparison of 16x16 Vedic Multipliers" International Journal of Computer Applications (0975 – 8887) Volume 21–No.6, May 2011

[3] Savita Patil, D.V.Manjunatha and Divya Kiran "Design of Speed and Power Efficient Multipliers Using Vedic Mathematics with VLSI Implementation" 2014 International Conference on Advances in Electronics, Computers and Communications (ICAECC).

[4] Poornima M, Shivaraj Kumar Patil, Shivukumar , Shridhar K P , Sanjay H "Implementation of Multiplier using Vedic Algorithm" International Journal of Innovative Technology and Exploring Engineering (IJITEE) ISSN: 2278-3075, Volume-2, Issue-6, May 2013.

[5] Sunil M, Ankith R D, Manjunatha G D and Premananda B S "Design and Implementation of Faster Parallel Prefix Kogge Stone Adder" ISSN 2319 – 2518 www.ijeetc.com Vol. 3, No. 1, January 2014© 2014 IJEETC.

[6] RaghavaGaripelly, P.Madhu Kiran, A.Santhosh Kumar "A Review on Reversible Logic Gates and their Implementation" International Journal of Emerging Technology and Advanced Engineering Website: www.ijetae.com (ISSN 2250-2459, ISO 9001:2008 Certified Journal, Volume 3, Issue 3, March 2013.

[7] VaijyanathKunchigi, Linganagouda Kulkarni, Subhash Kulkarni, High Speed and Area Efficient Vedic Multiplier, International Conference on Devices, Circuits and Systems (ICDCS), 2012.

[8] PrabirSaha, Arindam Banerjee, Partha Bhattacharyya, AnupDandapat, High Speed ASIC Design of Complex Multiplier Using Vedic Mathematics, Proceeding of the 2011 IEEE Students' Technology Symposium 14-16 January, 2011, IIT Kharagpur.

[9] AsmitaHaveliya, A Novel Design for High Speed Multiplier for Digital Signal Processing Applications (Ancient Indian Vedic mathematics approach), International Journal of Technology and Engineering System (IJTES), Vol.2, No.1, Jan -March, 2011.