# Dynamic Voltage Scaling Using FPGA

Amol Nagawade<sup>1</sup>

<sup>1</sup>PG Student of Electronics and Telecommunication Department, SVCOE, Indore, India.

Abstract— Emerging multicore processors are progressively power guarded by design ambiguity due to process dissimilarities. With the help of dynamic voltage scaling energy consumption can be reduced in microprocessor can be achieved without affecting the peak performance. In handy electronic devices processors are having a average load which is having a time-varying performance requirement. A methodology to vary DVS is by varying supply voltage of the processor's so that it ingests the least amount of energy by operating at the lowest performance level required by the dynamic software processes. It is a key method in developing the hardware characteristics of processors to decrease energy dissipation by dropping the operating frequency and supply voltage. To meet energetically varying performance requirement the method varies the voltage of processor below software control. The DVS algorithm are shown to be proficient to make dramatic energy storing while providing the essential peak average power in general purpose systems.

Keywords - FPGA, DVS, VCO, VHDL, Xilinx.

#### I. INTRODUCTION

Customers interest for progressively versatile yet superior sight and sound and correspondence items forces stringent limitations on the power utilization of individual inward parts. Of these, multipliers perform a standout amongst the most much of the time experienced math tasks in digital signal processors (DSPs). For installed applications, it has turned out to be basic to plan more power-mindful multipliers. Given their genuinely complex structure and interconnections, multipliers can display countless ways, bringing about generous glitch age and engendering. This deceptive exchanging action can be relieved by adjusting inner ways through a blend of design and transistor-level advancement methods.

Notwithstanding evening out inner way delays, dynamic power decrease can likewise be accomplished by observing the viable dynamic scope of the info operands in order to debilitate unused segments of the multiplier as well as truncate the yield item at the cost of diminished accuracy. For instance, in counterfeit neural system applications, the weight exactness utilized amid the learning stage is roughly twice that of the recovery stage .interestingly, the majority of the present full-custom DSPs and application-specific integrated circuits (ASICs) are intended for a settled most extreme word-length to suit the most dire outcome imaginable. Hence, a 8-bit duplication figured on a 32-bit Booth multiplier would bring about pointless exchanging action and power misfortune.

In Most applications depend on 8–16-b operands, the proposed multiplier is intended to perform single 16-b as well as performs single 8-b, or twin parallel 8-b duplication tasks. in some applications, 16 and 32 bit operands are send to littler duplication circuit with parallel task lessen control utilization and furthermore diminishes territory over head.

Because of the perplexing structure and interconnections, multipliers have extensive measure of unequal way which causes undesirable flag age and spread. This can be maintained a strategic distance from by appropriate inward adjusting through engineering and transistor level enhancement. by and large of multipliers, greatest word length is given. Henceforth little increases are done in vast multipliers, this causes undesirable exchanging movement and furthermore control utilization. So word length improvement is the best strategy in which 8-bit multiplier is reused for 16-bit and 32-bit augmentation. Here it is conceivable to fuse the pipelining for expanding the speed of the multiplier.

## II. OBJECTIVES

- To design a adaptive system according to workload.

- To reduce the circuit area and power consumption.

- To report the issues of fixed length ASIC's to avoid power loss and unnecessary switching activity.

### III. PROBLEM STATEMENT

To design and implement Input Oriented Dynamic Voltage Scaling Multiplier for effectively use of circuit area and to achieve lowest power consumption.

#### IV. LITERATURE SURVEY

X. Zhang, et.al.[1] ,Dynamic voltage/frequency scaling management unit configures the multiplier to operate at the proper precision and frequency. Adapting to the run-time workload of the targeted application, razor flip-flops together with a dithering voltage unit then configure the multiplier to achieve the lowest power consumption. an operands scheduler that re-arranges the input data, hence to determine the optimum voltage and frequency operating conditions for minimum power consumption.

K. Craig et.al.[2], This paper presents a 32 b, 90 nm data flow processor capable of executing arbitrary DSP algorithms using fine grained Dynamic Voltage Scaling (DVS) at the component level. For designs in the high performance design space, energy efficient operation reduce shot spots, lowers cooling costs, and avoids dark silicon issues. Many systems across this broad design space have applications that require high performance. However, due the varying nature of their applications, the workload requirements remain below this upper limit for the majority of their lifetime. Since different applications have varying workload requirements an energy efficient solution, such as dynamic voltage scaling (DVS), is needed. Dynamic voltage scaling is the conventional solution for adjusting energy consumption based on varying workload requirements.

S.R. Kuang et.al.[3], Power-efficient 16times, 16 configurable Booth multiplier (CBM) that supports single 16-b, single 8-b, or twin parallel 8-b multiplication operations is proposed. To efficiently reduce power consumption, a novel dynamic-range detector is developed to dynamically detect the effective dynamic ranges of two input operands. The detection result is used to not only pick the operand with smaller dynamic range for Booth encoding to increase the probability of partial products becoming zero but also deactivate the redundant switching activities in ineffective ranges as much as possible. Moreover, the output product of the proposed multiplier can be truncated to further decrease power consumption by sacrificing a bit of output precision.

K.-S. Chong et.al.[6],For embedded applications, it has become essential to design more power-aware multipliers. Given their fairly complex structure and interconnections, multipliers can exhibit a large number of unbalanced paths, resulting in substantial glitch generation and propagation. This spurious switching activity can be mitigated by balancing internal paths through a combination of architectural and transistor-level optimization techniques.

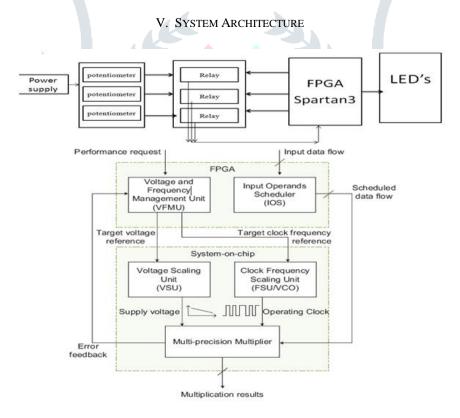

Fig1. System architecture diagram

#### VI. CONCLUSIONS

This system can operate on different voltage supply according to workload. By the scanning technique, it is possible to know about the range operands. Dynamic voltage scaling is effectively reduce the power consumption. By Frequency, voltage scaling overcome the unnecessary switching activity and power loss.

#### REFERENCES

- [1] X. Zhang, Farid and A. Bermak, "32 Bit X32 Bit Multiprecision Razor-Based Dynamic Voltage Scaling Multiplier With Operands Scheduler", IEEE Trans on very large scale integration (vlsi) system, vol.22,no.4,april 2014.

- K. Craig, Y. Shakhsheer, S.Arrabi, "A 32 b 90 nm Processor Implementing Panoptic DVS Achieving Energy Efficient Operation From Sub-Threshold to High Performance" IEEE Journal of solid -state circuits, vol. 49, no.2, February 2014.

- S.R. Kuang and J.-P. Wang, "Design of power-efficient configurable booth multiplier," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 57, no. 3, pp. 568-[3] 580, Mar. 2010.

- Benton H. Calhoun, Anantha P. Chandrakasan, "Ultra-Dynamic Voltage Scaling (UDVS) Using Sub-Threshold Operation and Local Voltage Dithering" [4] IEEE Journal of solid -state citcuits, vol.41,no.1, 2006.

- D. Ernst, N. Sung Kim, S. Das, "Razor: A Low-Power Pipeline Based on Circuit-Level Timing Speculation", IEEE Proceedings of the 36th International Symposium on Microarchitecture 2003.

- K.-S. Chong, B.-H. Gwee, and J. S. Chang, "A micro power low-voltage multiplier with reduced spurious switching," IEEE Trans. Very Large Scale Integer. (VLSI) Syst., vol. 13, no. 2, pp. 255–265, Feb. 2005.