# HIGH LOGIC DENSITY ARCHITECTURES OF FPGA USING HYBRID CLB'S

<sup>1</sup> MR. PABATHULA. MADHAVA RAO, <sup>2</sup> GAJULA.DEVI PRASANNA <sup>3</sup>YARRABAPU.GANESH KUMAR <sup>4</sup>JAMPALA.VENKATA JHANSI.

<sup>1</sup> Assistant Professor in Dept. Of ECE in Usha Rama College of Engineering and Technology in Telaprolu, Near Vijayawada City in Andhra Pradesh.

<sup>2,3,4</sup> B.Tech Final year In Dept. Of ECE in Usha Rama College of Engineering and Technology in Telaprolu, Near Vijayawada City in Andhra Pradesh.

Abstract: Field programmable gate arrays (FPGAs) are progressively utilized as the registering stage for quick and vitality effective execution of acknowledgment, mining, and inquiry applications. Surmised registering is one promising strategy for accomplishing vitality productivity. Contrasted and earlier chips away at rough registering, which target estimated processors and number juggling squares. Half and half configurable rationale square designs for field programmable entryway exhibits that contain a combination of request tables and solidified multiplexers are assessed toward the objective of higher rationale thickness and zone decrease.

Keywords— FPGA, Multiplexer logic element, Complex logic block, mapping technologies.

## **INTRODUCTION**

Field Programmable Gate Arrays (FPGAs) are an advantageous decision for low volume generation as they are anything but difficult to plan and program in a brief timeframe. Anyway the reconfigurability of FPGAs renders them a lot bigger, slower and more power devouring than their ASIC (Application Specific Integrated Circuits) partners [1]. ASICs, then again, have a higher non-repeating building (NRE) cost and higher time to advertise. Be that as it may, this issue is tended to by the presentation of Structured-ASICs which involve a variety of streamlined rationale components that can actualize wanted usefulness by making changes to a couple of upper cover layers [2] [3]. FPGA sellers like Altera and Xilinx have likewise begun making arrangement for relocating FPGA applications to Structured-ASIC. In such manner Altera has proposed a spotless movement approach from FPGA to Structured-ASIC while guaranteeing proportionality confirmation [4]. Yet, a FPGA totally looses its adaptability after its relocation to Structured-ASIC. An ASIF, then again, is diminished from FPGA like Structured ASIC yet it holds enough adaptability to actualize a lot of foreordained applications. A work based ASIF was at first displayed in [5] where creators have appeared for a lot of foreordained applications an ASIF is 81.5% littler than a unidirectional work based FPGA.

The MUX-based rationale hinders for the FPGAs have seen achievement in early business designs, for example, the Actel ACT-1/2/3 models, and productive mapping to these structures has been contemplated

[12] in the mid 1990s. Nonetheless, their utilization in business chips has wound down, maybe mostly because of the straightforwardness with which rationale capacities can be mapped into LUTs, disentangling the whole PC helped plan (CAD) stream. By and by, it is broadly comprehended that the LUTs are wasteful at actualizing MUXs, and that MUXs are much of the time utilized in rationale circuits. To underscore the wastefulness of LUTs actualizing MUXs, think about that a six info LUT (6-LUT) is basically a 64 to-1 MUX (to choose 1 of 64 truth-table columns) and 64-SRAMconfiguration cells, yet it can just understand a 4-to-1 MUX (4 information + 2 select = 6 inputs). In this paper, we present a six-input LE dependent on a 4-to-1 MUX, MUX4, that can understand a subset of six-input Boolean rationale capacities, and another crossover complex rationale square (CLB) that contains a blend of MUX4s and 6-LUTs. A Hybrid configurable rationale square models for field programmable entryway clusters that contain a blend of query tables and solidified multiplexers are assessed toward the objective of higher rationale thickness and region decrease.

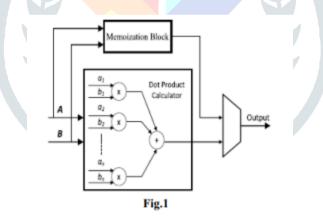

#### AN APPROXIMATE COMPUTING METHODOLOGY

The memorization design generator contains a retention wrapper generator that produces the building squares required for remembrance. It takes likeness measure, edge (Th), client information sources, and client determination, which are available in the design record, as the information. The likeness measure is characterized by the client to look at two transiently dispersed data sources; limit (Th) is the edge an incentive inside which the aftereffect of closeness estimation must exist.

The memoization technique that the client chooses is taken as an information by means of client determination parameter. Contingent upon this determination, RTL wrapper is produced for either thestatic retention or the dynamic memoization. The client provided data, for example, similitude measure, is best chosen by the client as he/she is progressively mindful of the area of utilization to which the proposed memoization-based surmised processing is being connected. Here, the flag is utilized just in unique memoization wrapper, while the others are basic flags in both the designs.

#### HYBRID LUT/MULTIPLEXER FPGA LOGIC ARCHITECTURES

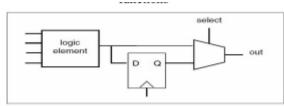

Not at all like a common rationale entryway, the capacity spoken to by the rationale component can be changed by changing the estimations of the bits spared in the SRAM. Subsequently, the n-input rationale component can speak to capacities.

Figure-2Programming a Lookup Table

A reason part has four wellsprings of data. The delay in the question table is free of the bits secured in the SRAM, so the deferral through the justification part is the equivalent for all limits. Hugeness of this is, for example, an inquiry table based method of reasoning segment will demonstrate a comparative deferment for a 4-input XOR and a 4-input NAND. In distinction, a 4-input XOR worked with static CMOS method of reasoning is much slower than a 4-input NAND. Clearly, the static method of reasoning passage is conventionally quick than the justification segment. Method of reasoning parts contain registers, flip-droops and bolts and furthermore combinational justification. A flip-tumble or snare is little diverged from the combinational justification part, so it has criticalness to add it to the combinational method of reasoning segment. Using a substitute cell for the memory segment would basically take up coordinating resources. The memory segment is associated with the yield, paying little mind to whether it stores a given regard is constrained by its clock and enable sources of info. In this paper, we propose consolidating (a couple) hardened multiplexers (MUXs) in the FPGA basis blocks that induce extending silicon region capability and justification thickness. The MUX based justification frustrates for the FPGAs have seen triumph in early plans of action, for instance, the Actel, ACT1/2/3 plans, and gainful mapping to these structures has been inspected in the mid 1990s. Regardless, their usage in business chips has slowed down, possibly not completely as a result of the straightforwardness with which basis limits can be mapped into LUTs, constraining the entire PC helped plan (CAD) stream. Regardless, it is extensively appreciated that the LUTs are inefficient at realizing MUXs, and that MUXs are once in a while used as a piece of method of reasoning circuits. To underscore the inefficiency of LUTs realizing MUXs, consider that a six data LUT (6-LUT) is fundamentally a 64-to-1 MUX (to pick 1 of 64 truth-table lines) and 64-SRAM plan cells, yet it can simply comprehend a 4-to-1 MUX (4 data+2 select=6 inputs). In this endeavor, we show a six-input LE in light of a 4-to-1 MUX, MUX4, that can comprehend a subset of six-input Boolean basis limits, and another mutt complex justification piece (CLB) that has a mix of MUX4s and 6-LUTs. The proposed MUX4s are little differentiated and a 6-LUT (15% of 6-LUT region), and can capably plot  $\{2,3\}$ -data and some  $\{4,5,6\}$ -input limits.

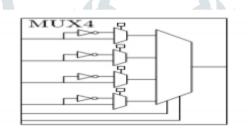

#### MUX4: 4-to-1 Multiplexer Logic Element

The MUX4 LE showed up in Figure. 3 contains a 4-to-1 MUX with optional inversion on its data sources that license the affirmation of any {2,3}-input work, some {4,5}-input limits, and one 6-input work a 4-to-1 MUX itself with optional inversion on the data inputs. A 4-to-1 MUX matches the data stick count of a 6-LUT, mulling over sensible examinations concerning the system and intra bunch coordinating. Any two-input Boolean limit can be viably executed in the MUX4: the two limit data sources can be appended to the select lines and reality table regards (reason 0or basis can be coordinated to the data contributions as requirements be. For three-input limits; think about that Shannon rot around one variable produces cofactors with at most two components. A minute deterioration of the co-factors around one of their two remarkable components produces cofactors with at most one variable. Such singlevariable cofactors can be reinforced to the data inputs (the optional inversion may be required), with the deterioration factors empowering the select wellsprings of information. In addition, components of beyond what four wellsprings of information can be executed in the MUX4 as long as Shannon disintegration concerning any two information sources produces cofactors with at most one data.

Figure.3. MUX4 LE depicting optional data input inversions

Two gatherings of plans were made: Without fracturable LEs and With fracturable LEs. The fracturable LEs insinuate a plan part on which no less than one method of reasoning limits can be on the other hand mapped. Nonfracturable LEs suggest a plan part on which only a solitary method of reasoning work is mapped. In the nonfracturable plans, the MUX4 segment showed up in Fig. 3 is used together with nonfracturable 6-LUTs. This part has an undefined number of commitments from a 6-LUT crediting for sensible examination with respect to the data accessibility. For the fracturable plan, we think about an eight-input LE, immovably organized with the flexible method of reasoning module in late Altera Stratix FPGA families. For the MUX4 variety, Dual MUX4, we use two MUX4s inside a singular eight-input LE. In the setup, showed up in Fig. 4, the two MUX4s are wired to have dedicated select wellsprings of data and shared data inputs. This game plan empowers this structure to layout free (no regular wellsprings of data) three-input limits, while greater limits may be mapped subject to the common commitments between the two limits. A designing in which a 4-to-1 MUX (MUX4) is split into two tinier 2-to-1 MUXs was considered.

Figure.4. Dual MUX4 LE that utilizes dedicated select inputs and shared data Inputs

Preparing with memory stages are generally used to give the benefit of hardware reconfigurability. Reconfigurable enlisting stages offer central focuses the extent that diminished layout cost, early time toexhibit, snappy prototyping and easily movable gear systems. FPGAs demonstrate an outstanding reconfigurable enlisting stage for executing propelled circuits. They take after a totally spatial handling model. The fundamental structure of the FPGAs has continued involving two-dimensional bunch of Configurable Logic squares (CLBs) and a programmable interconnect organize. FPGA execution and power dispersal is, as it were, overpowered by the explain programmable interconnect (PI) plan. A ground-breaking strategy for diminishing the impact of the PI plan in FPGA is to put little LUTs in closeness (implied as groups). Due to the benefits of FPGA building, major FPGA shippers have combined it in their business things. Examinations have moreover been made to diminish the overhead in light of PI in fine-grained FPGAs by mapping greater multi-input multi-yield LUTs to embedded memory pieces. Notwithstanding the way that it takes after a practically identical spatial preparing model, some bit of the reason limits are executed using embedded memory squares while the remainder of the part is recognized using humbler LUTs. Such a heterogeneous mapping can improve the range and execution by reducing the dedication of programmable interconnects. Notwithstanding the essentially spatial figuring model of FPGA, a reconfigurable preparing stage that uses a transient enlisting model (or a mix of both common and spatial) has moreover been looked into with respect to upgrading execution and imperativeness over normal FPGA. These stages, suggested as Memory Based Computing (MBC), use thick two-dimensional memory show to store the LUTs. Such frameworks rely upon breaking a complex limit (f) into little sub-limits; addressing the sub-limits as into multi-input, multi-yield LUTs in the memory display; and surveying the limit f over various cycles. MBC can use on the high thickness, low power and unrivaled focal points of nanoscale memory. Each figuring segment melds a twodimensional memory bunch for securing LUTs, a little controller for sequencing appraisal of sub-limits and a game plan of fleeting registers to hold the widely appealing yields from solitary allocations. A fast, neighborhood guiding framework inside each figuring square makes the location for LUT get to. Diverse such handling parts can be spatially related using FPGA-like programmable interconnect configuration to engage mapping of broad limits. The close-by time-multiplexed execution inside the enrolling parts can diminish the essential of programmable interconnects provoking considerable change in imperativeness concede thing and better adaptability of execution transversely over development periods.

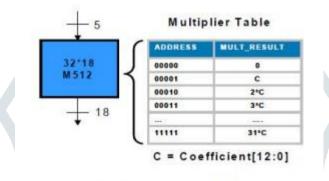

Fragile multipliers are an incredibly versatile other alternative to using DSP squares. Instead of executing a combinatorial reason multiplier, they utilize a novel use in perspective on a deficient lookinto table (LUT) use of the expansion task, where the LUT is realized in the memory squares. Sensitive multipliers increase by a factor of in the region of 2 and 15 the amount of multipliers open. By downloading unmistakable coefficient LUTs, various plans of multipliers and adders are made. Figure underneath exhibits direct Soft Multiplier completed with a M512 (32\*18) RAM square. The 5 bits width input data is driving the location transport of a memory and demonstrating a LUT territory that has the 18 bit outcome. The LUT covers all the expansion mixes of 5 bits of data with 13 bits coefficient.

Fig 6: Simple soft multiplier

An ordinary query table (LUT)- based multiplier according to underneath figure, where A will be a fixed coefficient, and X is an info word to be increased with A. Expecting X to be a positive parallel number of word length L, there can be 2L conceivable estimations of X, and as needs be, there can be 2L conceivable estimations of item  $C = A \cdot X$ .

Fig 7: Conventional LUT-based multiplier.

In this manner, for memory-based augmentation, a LUT of 2L words, comprising of precomputed item esteems comparing to every single imaginable estimation of X, is expectedly utilized. The item word A•Xi is put away at the area Xi for  $0 \le Xi \le 2 L-1$ , with the end goal that if a L-bit twofold estimation of Xi is utilized as the location for the LUT, at that point the comparing item esteem A•Xi is accessible as its yield.

#### FPGA Area Model:

Regardless of the way that choosing the region of a MUX4 part in regard to a 6-LUT is fundamental, we need to in like manner dissect overall FPGA go considering the amount of CLB tiles, zone overheads inside the CLB and directing district per CLB. All through this paper, overall FPGA district was surveyed tolerating that, per tile, half of the locale is cover bundle and intra bunch directing, 30% of the range is used for LUTs, and 20% for registers and diverse different reason, following Anderson and Wang and a private correspondence. Note that this 50%– 30%– 20% model is a check in perspective on a standard full FPGA plan where-by the controlling and internal CLB crossbars are improved toward 6-LUTs. Formation of a progressed FPGA utilizing our new MUX4 segments would indeed change said illustrate. Nevertheless, propelling the entire guiding building toward our MUX4 varieties, estimating the coordinating structure, and closing the hover by making a progressively exact model is out of the degree of this work. Using this model, we can make reference to some target certainties about the creamer CLB designing.

# **RESULTS**

#### Simulation results

|                   |       | 318.328 ns                           |  |  |  |  |  |  |  |  |  |

|-------------------|-------|--------------------------------------|--|--|--|--|--|--|--|--|--|

| Name              | Value | 0 ns 1200 ns 1400 ns 1600 ns 1800 ns |  |  |  |  |  |  |  |  |  |

| ી <sub>α</sub> γ0 | 0     |                                      |  |  |  |  |  |  |  |  |  |

| liα y1            |       |                                      |  |  |  |  |  |  |  |  |  |

| 🕨 📷 a[3:0]        | 1100  | 0000 1100                            |  |  |  |  |  |  |  |  |  |

| 🕨 📷 s0[1:0]       | 00    | 00                                   |  |  |  |  |  |  |  |  |  |

| 🕨 📷 s1[1:0]       | 01    | 00 01                                |  |  |  |  |  |  |  |  |  |

| 🐻 is1             | 1     |                                      |  |  |  |  |  |  |  |  |  |

| 🐻 is0             | 1     |                                      |  |  |  |  |  |  |  |  |  |

| 16 is2            | 1     |                                      |  |  |  |  |  |  |  |  |  |

|                   |       |                                      |  |  |  |  |  |  |  |  |  |

|                   |       |                                      |  |  |  |  |  |  |  |  |  |

|                   |       |                                      |  |  |  |  |  |  |  |  |  |

|                   |       |                                      |  |  |  |  |  |  |  |  |  |

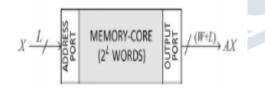

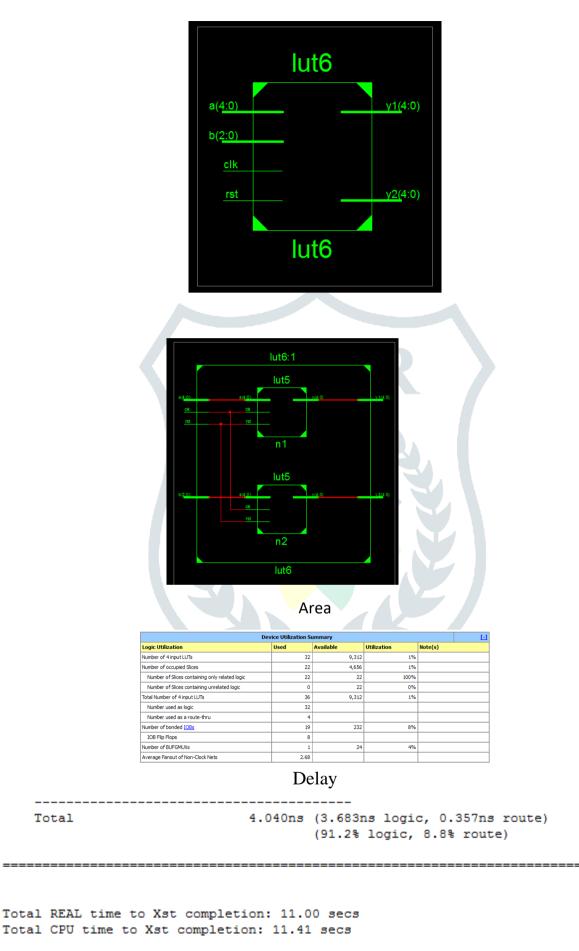

Synthesis Results: RTL schematic:

Power

| Α                              | В             | С      | D                                | E         | F             | G           | Н               | T. | J      | К         | L           | М           | Ν           |

|--------------------------------|---------------|--------|----------------------------------|-----------|---------------|-------------|-----------------|----|--------|-----------|-------------|-------------|-------------|

| Device                         |               |        | On-Chip                          | Power (W) | Used          | Available   | Utilization (%) |    | Supply | Summary   | Total       | Dynamic     | Quiescent   |

| Family                         | Spartan3e     |        | Clocks                           | 0.000     | 1             | -           |                 |    | Source | Voltage   | Current (A) | Current (A) | Current (A) |

| Part                           | xc3s500e      |        | Logic                            | 0.000     | 26            |             | 0               |    | Vccint | 1.200     | 0.026       | 0.000       | 0.026       |

| Package                        | fg320         |        | Signals                          | 0.000     | 38            |             |                 |    | Vccaux | 2.500     | 0.018       | 0.000       | 0.018       |

| Temp Grade                     | Commercial    | ~      | IOs                              | 0.000     | 19            | 232         | 8               |    | Vcco25 | 2.500     | 0.002       | 0.000       | 0.002       |

| Process                        | Typical       | ~      | Leakage                          | 0.081     |               |             |                 |    |        |           |             |             |             |

| Speed Grade                    | -5            |        | Total                            | 0.081     |               |             |                 |    |        |           | Total       | Dynamic     | Quiescent   |

|                                |               | _      |                                  |           |               |             |                 |    | Supply | Power (W) | 0.081       | 0.000       | 0.081       |

| Environment Effective T        |               |        |                                  |           | Effective TJA | Max Ambient | Junction Temp   |    |        |           |             |             |             |

| Ambient Temp (C) 25.0          |               |        | Thermal Properties (C/W) (C) (C) |           |               |             |                 |    |        |           |             |             |             |

| Use custom TJA?                |               | $\sim$ |                                  |           | 26.1          | 82.9        | 27.1            |    |        |           |             |             |             |

| Custom TJA (C/W)               | NA            |        |                                  |           |               |             |                 |    |        |           |             |             |             |

| Airflow (LFM)                  | 0             | ~      |                                  |           |               |             |                 |    |        |           |             |             |             |

| Characterization<br>PRODUCTION | v1.2.06-23-09 |        |                                  |           |               |             |                 |    |        |           |             |             |             |

#### **Conclusion**

We have proposed another half breed CLB engineering containing MUX4 hard MUX components for proficient are and mapping to these models. Weighting of MUX4-embeddable capacities with our Mux Map method joined with a select mapping system furnished guide to circuits with low normal MUX4-embeddable proportions. In expansion work the counter symmetric item coding (APC) and odd-multiplestorage (OMS) procedures for query table (LUT) structure for memory-based multipliers to be utilized in computerized flag handling applications. Every one of these strategies results in the decrease of the LUT estimate by a factor of two. In this concise, we present an alternate type of APC and a changed OMS plot, so as to consolidate them for proficient memory-based increase.

## REFERENCES

I. Kuon and J. Rose, "Measuring the gap between FPGAs and ASICs," in Proceedings of the 2006 ACM/SIGDA 14th international symposium on Field programmable gate arrays. ACM New York, NY, USA, 2006, pp. 21–30.

[2] K. Wu and Y. Tsai, "Structured ASIC, Evolution or Revolution," April 2004, pp. 103-106.

[3] T. Okamoto, T. Kimoto, and N. Maeda, "Design Methodology and Tools for NEC Electronics Structured ASIC," April 2004, pp. 90–96.

[4] J. Pistorius, M. Hutton, J. Schleicher, M. Iotov, E. Julias, and K. Tharmalignam, "Equivalence Verification of FPGA and Structured ASIC Implementations," August 2007, pp. 423–428.

[5] H. Parvez, Z. Marrakchi, and H. Mehrez, "ASIF: Application Specific Inflexible FPGA," in International Conference on Field-Programmable Technology, 2009. FPT 2009, 2009, pp. 112– 119.

[6] V. Betz and J. Rose, "VPR: A New Packing Placement and Routing Tool for FPGA research," International Workshop on FPGA, pp. 213–22, 1997.

[7] G. Lemieux, E. Lee, M. Tom, and A. Yu, "Directional and singledriver wires in fpga interconnect," in IEEE Conference on FPT, 2004, pp. 41–48.

[8] Z. Marrakchi, H. Mrabet, E. Amouri, and H. Mehrez, "Efficient tree topology for fpga interconnect network," in ACM Great Lakes Symposium on VLSI, 2008, pp. 321–326.