# CASCADED SEVEN LEVEL H-BRIDGE INVERTER WITH FILTER AND BOOST CONVERTER

# Mrs. Mahadevi S N Assistant Professor, Department of EEE PDA of Engineering, Kalburgi, Karnataka, India

*Abstract*- This paper presents a study of seven-Level Cascaded H – bridge (CHB) Inverter. Advantages of CHB inverter are low harmonic distortion, reduced number of switches and suppression of switching losses. They typically synthesize the stair –case voltage waveform (from several dc sources) which has better harmonic spectrum. This paper targets to outspread the information about the working of seven level Cascaded H-Bridge MLI topology with DC/DC Boost Converter for constant DC Source. The output voltage is the sum of the voltage that is generated by each bridge. The switching angle employs Sinusoidal Pulse Width Modulation technique. With this method THD is curtailed. This configuration incorporates Boost Converter in the input side which augments the fundamental output voltage. It also has output filter and thus resultant wave is nearer to the sine wave. Outcomes are verified and observed that yields efficiency around 82%. The analysis of proposed topology has Intended successfully by using MATLAB/Simulink.

# IndexTerms- Multi level Inverter (MLI), Pulse Width Modulation (PWM), Cascaded H-Bridge (CHB), Total Harmonic Distortion (THD)

# I. Introduction

Power Electronics is the art of converting electrical energy from one form to another in an efficient, clean, compact, and robust manner for convenient utilization. It has found an important place in modern technology being core of power and energy control. It is the technology associated with efficient conversion, control and conditioning of electric power from its available input into the desired output form. There are many limitations in extracting power from renewable energy resources. To minimize the power demand and scarcity we have to improve the power extracting methods. Multilevel inverter is used to extract power from solar cells. It synthesizes the desired ac output waveform from several dc sources. This paper focuses on improving the efficiency of the multilevel inverter and quality of output voltage waveform. Seven level reduced switches topology has been implemented with only seven switches. Fundamental Switching scheme and Selective Harmonics Elimination were implemented to reduce the Total Harmonics Distortion (THD) value. Selective Harmonics Elimination Stepped Waveform (SHESW) method is implemented to eliminate the lower order harmonics. Fundamental switching scheme is used to control the power electronics switches in the inverter. The proposed topology is suitable for any number of levels. The harmonic reduction is achieved by selecting appropriate switching angles. It shows hope to reduce initial cost and complexity hence it is apt for industrial applications. Cascade Multilevel Inverters are very popular and have many applications in electric utility and for industrial drives. When these inverters are used for industrial drive directly, the THD contents in output voltage of inverters is very significant index as the performance of drive depends very much on the quality of voltage applied to drive.

The concept of multilevel converters has been introduced since 1975 [4]. The term multilevel began with the three-level converter [5]. Subsequently, several multilevel converter topologies have been developed [6-13]. However, the elementary concept of a multilevel converter to achieve higher power is to use a series of power semiconductor switches with several lower voltage dc sources to perform the power conversion by synthesizing a staircase voltage waveform.

# II CASCADED H BRIDGE MULTILEVEL INVERTER

Multilevel converters are mainly utilized to synthesis a desired single- or three-phase voltage waveform. The desired multistaircase output voltage is obtained by combining several dc voltage sources. Solar cells, fuel cells, batteries and ultra-capacitors are the most common independent sources used. One important application of multilevel converters is focused on medium and high-power conversion. Nowadays, there exist three commercial topologies of multilevel voltage-source inverters: neutral point clamped (NPC), cascaded H-bridge (CHB), and flying capacitors (FCs). Among these inverter topologies, cascaded multilevel inverter reaches the higher output voltage and power levels (13.8 kV, 30 MVA) and the higher reliability due to its modular topology.

Diode-clamped multilevel converters are used in conventional high-power ac motor drive applications like conveyors, pumps, fans, and mills. They are also utilized in oil, gas, metals, power, mining, water, marine, and chemical industries. They have also been reported to be used in a back-to-back configuration for regenerative applications. Flying capacitor multilevel converters have been used in high-bandwidth high-switching frequency applications such as medium-voltage traction drives. Finally, cascaded H-bridge multilevel converters have been applied where high power and power quality are essential, for example, static synchronous compensators active filter and reactive power compensation applications, photovoltaic power conversion, uninterruptible power supplies, and magnetic resonance imaging. Furthermore, one of the growing applications for multilevel motor drives is electric and hybrid power trains.

#### © 2019 JETIR May 2019, Volume 6, Issue 5

For increasing voltage levels the number of switches also will increase in number. Hence the voltage stresses and switching losses will increase and the circuit will become complex. By using the proposed topology number of switches will reduce significantly and hence the efficiency will improve. In high power applications, the harmonic content of the output waveforms has to be reduced as much as possible in order to avoid distortion in the grid and to reach the maximum energy efficiency. The challenge associated with techniques is to obtain the analytical solutions of the non-linear transcendental equations that contain trigonometric

#### **III. SEVEN LEVEL CASCADED H-BRIDGE MULTILEVEL INVERTER STRUCTURE**

Conventional cascaded multilevel inverters are one of the most important topologies in the family of multilevel and multi-pulse inverters. The cascade topology allows the use of several levels of DC voltages to synthesize a desired AC voltage. The DC levels are considered to be identical since all of them are fuel cells or photovoltaics, batteries, etc. [20]. It requires least number of components compared to diode-clamped and flying capacitors type multilevel inverters and no specially designed transformer is needed as compared to multi pulse inverter.

Since this topology consist of series power conversion cells, the voltage and power level may be easily scaled. The concept of this inverter is based on connecting H-bridge inverters in series to get a sinusoidal voltage output. The output voltage is the sum of the voltage that is generated by each cell. The number of output voltage levels are 2n+1, where *n* is the number of cells. The switching angles can be chosen in such a way that the total harmonic distortion is minimized. An *n* level cascaded H-bridge multilevel inverter needs 2(n-1) switching devices where *n* is the number of the output voltage level.

### Fig.1 Seven level CHB inverter

Cascade topology proposed in [21] uses multiple dc levels, which instead of being identical in value are multiples of each other. It also uses a combination of fundamental frequency switching for some of the levels and PWM switching for part of the levels to achieve the output voltage waveform. This approach enables a wider diversity of output voltage magnitudes; however, it also results in unequal voltage and current ratings for each of the levels and loses the advantage of being able to use identical, modular units for each level.

# IV. THE SUGGESTED MULTILEVEL INVERTER

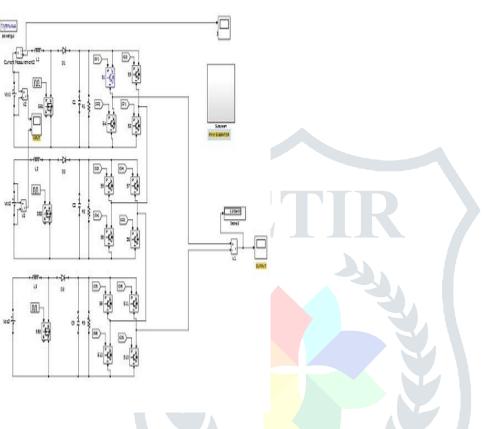

The single phase cascaded seven level inverter topology [22] has been proposed in Fig.1. The circuit consists of sixteen main switches in four series connected H-bridge configuration S1~S4, S5~S8, S9~S12. The number of dc sources are four so the output voltage of the cascaded multilevel inverter is Vo=V1+V2+V3. The output waveforms of multilevel inverters are in a stepped waveform therefore they have reduced harmonics compared to a square wave inverter.

Each separate dc source (SDCS) is connected to a single-phase full-bridge, or H-bridge inverter. Each inverter level can generate three different voltage outputs,  $+V_{dc}$ , 0, and  $-V_{dc}$  by connecting the dc source to the ac output by different combinations of the four switches,  $S_1$ ,  $S_2$ ,  $S_3$ , and  $S_4$ . To obtain  $+V_{dc}$ , switches  $S_1$  and  $S_2$  are turned on, whereas  $-V_{dc}$  can be obtained by turning on switches  $S_3$  and  $S_4$ . By turning on  $S_1$  and  $S_2$  or  $S_3$  and  $S_4$ , the output voltage is 0. Similarly S5 and S6 for  $+V_{dc}$ , switches  $S_7$  and  $S_8$  are turned on for  $-V_{dc}$ . The ac outputs of each of the different full-bridge inverter levels are connected in series such that the synthesized voltage waveform is the sum of the inverter outputs.

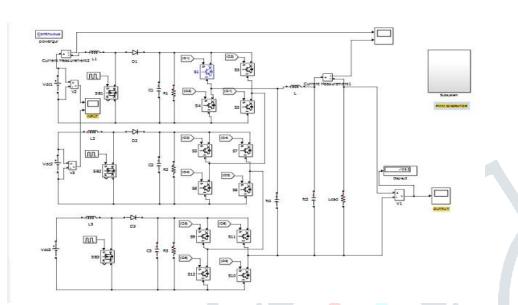

A single-phase structure of a seven level cascaded inverter with DC/DC boost converter is illustrated in Figure 3. The operation of this topology is as same as conventional 7-level CHB, difference lies in the voltage level which is due to presence of DC/DC boost converter which boosts the input voltage the designed value.

## Fig.2 Seven-level CHB MLI with DC/DC Boost Converter

# V. PROPOSAL OF PROJECTED TOPOLOGY

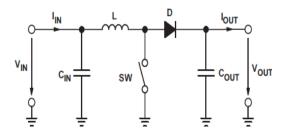

### 5.1 DC/DC BOOST CONVERTER

Boost converter steps up the input voltage magnitude to a required output voltage magnitude without the use of a transformer [23]. The main components of a boost converter are an inductor, a diode and a high frequency switch as shown in fig 3. These in a coordinated manner supply power to the load at a voltage greater than the input voltage magnitude.

Fig.3 Boost Converter power stage

# **Inductor Selection**

$$L = \frac{\mathrm{Vi}_{*}(\mathrm{Vo} - \mathrm{Vi})}{\mathrm{Fs}_{*}\mathrm{Vo}_{*}\Delta\mathrm{IL}}\dots\dots(1)$$

# Output Capacitor Selection

Best practice is to use low ESR capacitors to minimize the ripple on the output voltage. Ceramic capacitors are a good choice.

$$Cb = \frac{Po}{\omega Vo} \dots (3)$$

Po= output power; Cb= input capacitor

For a good practice choose Cf= 4-5% of Cb

Here input voltage is 12+12+12=36V. Due to the presence of DC/DC boost Converter voltage will increase to 48+48+48=144V.

#### **5.2 Measured Parameters**

| 1.                                                                                  | Input            | 36V     |  |

|-------------------------------------------------------------------------------------|------------------|---------|--|

|                                                                                     | voltage          |         |  |

| 2.                                                                                  | Output           | 131V    |  |

|                                                                                     | voltage          |         |  |

| 3.                                                                                  | Input            | 11.2A   |  |

|                                                                                     | current          |         |  |

| 4.                                                                                  | Output           | 2.50A   |  |

|                                                                                     | current          |         |  |

| 5.                                                                                  | Input            | 403.2 W |  |

|                                                                                     | power            |         |  |

| 6.                                                                                  | Output           | 327.5 W |  |

|                                                                                     | power            |         |  |

| Table 4 Inverter Parameters                                                         |                  |         |  |

|                                                                                     |                  |         |  |

|                                                                                     |                  |         |  |

|                                                                                     |                  |         |  |

| Efficiency= $\underline{output power}$ = $\underline{327.5}$ =<br>Input power 403.2 |                  |         |  |

|                                                                                     | mput power 405.2 |         |  |

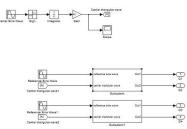

#### 5.3 firing pulse analysis

Pulse-width modulation (PWM) is the basis for control in power electronics. The theoretically zero rise and fall time of an ideal PWM waveform represents a preferred way of driving modern semiconductor power devices. With the exception of some resonant converters, the vast majority of power electronic circuits are controlled by PWM signals of various forms. Although other considerations, such as parasitic ringing and electromagnetic interference (EMI) emission, may impose an upper limit on the turn-on and turn-off speed in practical conditions, the resulting finite rise and fall time can be ignored in the analysis of PWM signals and processes in most cases.

### VI. SIMULATION RESULTS

### 6.1 Modeling of CHB MLI

Fig.5 shows the Matlab/Simulink Model of seven level Cascaded H-Bridge MLI with DC/DC Boost Converter. Each H-bridge DC voltage is 12 V. Hence total input is 36 volts

Fig.5 DC/DC Boosted Seven level Inverter with Filter

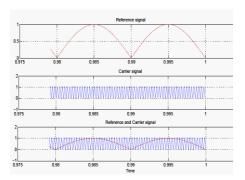

Fig.6 shows the Matlab/Simulink pulse generator model. The Switches are turned ON and turned OFF with a phase delay of 0 and –pi/3 respectively. Fig.6 shows Simulated Reference and Carrier Wave

Fig. 6 Pulse Generator Model

Fig.7 Simulated Reference and Carrier Wave

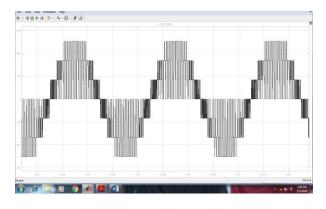

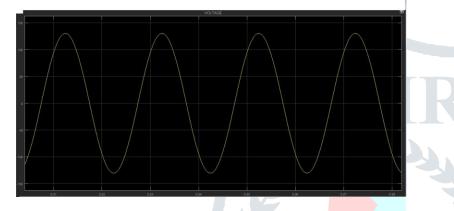

Fig.8 shows the Matlab/Simulink model Boosted 7-level CHB MLI output voltage without filter, having Magnitude of 132V in staircase(stepped) AC, to get pure sine wave an LC filter is added which is shown in figure 9

Fig. 8 Basic seven level CHB MLI output voltage

Fig. 9 Basic Seven level CHB MLI output voltage with DC/DC boost converter and filter

#### 6.2 THD Analysis

Total harmonic distortion, or THD, is the summation of all harmonic components of the voltage or current waveform compared against the fundamental component of the voltage or current wave. In this method the switching angles for switches should be calculated in such a way that the dominant harmonics are eliminated (minimized). The THD will be decreased by increasing the number of levels. It is obvious that an output voltage with low THD is desirable, but increasing the number of levels more hardware, also the control will be more complicated.

$$\% THD = \frac{\sqrt{V2^2 + V3^2 + V4^2 + V5^2 + V6^2 \dots Nn^2}}{V_2} * 100 \dots (4)$$

Where,  $V_1$  = Fundamental Voltage magnitude

- V<sub>2 =</sub> Magnitude of 2<sup>nd</sup> Harmonic

- $V_{3}$  = Magnitude of 3<sup>rd</sup> Harmonic

- $V_{n =}$  Magnitude of  $n^{th}$  Harmonic

The formula above shows the calculation for THD on a voltage signal. The end result is a percentage comparing the harmonic components to the fundamental component of a signal. The higher the percentage, the more distortion that is present on the mains signal.

#### VII. CONCLUSION

It has been observed from the simulation results that the overall efficiency of the developed seven level inverter is 81% which is more than the conventional DC to AC inverter. The two-level inverter has the lowest cost and weight in comparison with the other topologies. But it has very high THD and it is not practical to have an output voltage with high such THD. The design of the 7-level multilevel inverters seems to be better than the 11-level multilevel inverters. By increasing the number of levels, the cost and weight of the multilevel inverter will be increased. So this topology is well suited for industrial drives.

#### REFERENCES

[1]. R.H. Baker, Electric Power Converter, U.S. Patent Number 3,867,643, February 1975.

[2]. R.H. Baker, High-Voltage Converter Circuit, U.S. Patent Number 4,203,151, May 1980.

[3]. Kelaiaia Mounia Samira, Labar Hocine, Bounaya Kamel, and Kelaiaia Samia "Effect of Flaying Capacitors on Improving the 4 Level Three-Cell Inverter" *World Academy of Science, Engineering and Technology 30 2009.*

[4]. Javier Pereda, Student Member, IEEE, and Juan Dixon, Senior Member, IEEE "High Frequency Link: A Solution for Using Only One DC Source in Asymmetric Cascaded Multilevel Inverters" *IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS*, VOL. 58, NO. 9, SEPTEMBER 2011

[5]. Yushan Liu, Student Member, IEEE, Baoming Ge, Member, IEEE, Haitham Abu-Rub, Senior Member, IEEE, and Fang Zheng Peng, Fellow, IEEE "An Effective Control Method for Three-Phase Quasi-Z-Source Cascaded Multilevel Inverter Based Grid-Tie Photovoltaic Power System" *IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS*

[6]. Xiaomin Kou, Student Member, IEEE, Keith A. Corzine, Member, IEEE, and Yakov L. Familiant, Student Member, IEEE "Full Binary Combination Schema for Floating Voltage Source Multilevel Inverters" *IEEE TRANSACTIONS ON POWER ELECTRONICS*, VOL. 17, NO. 6, NOVEMBER 2002

[7].Maria Imecs, Andrzej M. Trzynadlowski, Fellow, IEEE, Ioan I. Incze, and Csaba Szabo "Vector Control Schemes for Tandem-Converter Fed Induction Motor Drives" *IEEE TRANSACTIONS ON POWER ELECTRONICS*, VOL. 20, NO. 2, MARCH 2005

[8]. Madhav D. Manjrekar Thomas A. Lipo A hybrid multilevel inverter topology for drive applications

[9]. Leon M. Tolbert, Senior Member, IEEE, Fang Zheng Peng, Senior Member, IEEE, and Thomas G. Habetler, Senior Member, IEEE "A Multilevel Converter-Based Universal Power Conditioner" *IEEE TRANSACTIONS ON INDUSTRY APPLICATIONS*, VOL. 36, NO. 2, MARCH/APRIL 2000

[10]. Leon M. Tolbert, Senior Member, IEEE, Fang Zheng Peng, Senior Member, IEEE and Thomas G. Habetler, Senior Member, IEEE "Multilevel Converters for Large Electric Drives" *IEEE TRANSACTIONS ON INDUSTRY APPLICATIONS*, VOL. 35, NO. 1, JANUARY/FEBRUARY 1999

[11]. M.S.Sivagamasundari, 1 P.Melba Mary2 "A Single Phase Eleven Level Cascaded H-Bridge Multilevel Inverter for Photovoltaic Systems Using Multicarrier Pwm" *International Journal of Modern Engineering Research (IJMER)* www.ijmer.com Vol.2, Issue.6, Nov-Dec. 2012 pp-4703-4709 ISSN: 2249-6645

[12]. M.S.Sivagamasundari1, Dr.P.Melba Mary2 "Analysis of Cascaded Five Level Multilevel InverterUsingHybrid PulseWidth Modulation" *International Journal of Emerging Technology and Advanced Engineering* ISSN 2250-2459, ISO 9001:2008 Certified Journal, Volume 3, Issue 4, April 2013

[13]. Mahrous Ahmed, Ibrahim Taha, Sherif Ghoneim "Multilevel Inverter with Natural Balancing of DC Sources for PV System Applications" / *International Journal of Engineering Research and Applications (IJERA)* ISSN: 2248-9622 www.ijera.com Vol. 3, Issue 1, January -February 2013

[14]. Thierry A. Meynard, Member, IEEE, Henri Foch, Philippe Thomas, Jacques Courault, Roland Jakob, and Manfred Nahrstaedt "Multicell Converters: Basic Concepts and Industry Applications" *IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS*, VOL. 49, NO. 5, OCTOBER 2002

[15]. P. Satheesh Kumar, Dr. S. P. Natarajan, Dr. Alamelu Nachiappan , Dr. B. Shanthi "Performance Evaluation of Seven Level Modified CHB Multilevel Inverter for Various PWM Strategies" *International Journal of Modern Engineering Research (IJMER)* Vol. 3, Issue. 5, Sep - Oct. 2013 pp-2758-2766 ISSN: 2249-6645

[16]. F. Khoucha, A. Ales, A. Khoudiri, K. Marouani, M.E.H. Benbouzid and A. Kheloui "A 7-Level Single DC Source Cascaded H-Bridge Multilevel Inverters Control Using Hybrid Modulation" *XIX International Conference on Electrical Machines* - *ICEM 2010*, Rome

[17]. A. Nabae, I. Takahashi, and H. Akagi, "A New Neutral-Point Clamped PWM Inverter," *Proceedings of the Industry Applications Society Conference*, pages 761-766, September/October 1980.

[18]. Xiaoming Yuan, Member, IEEE, and Ivo Barbi, Senior Member, IEEE "Fundamentals of a New Diode Clamping Multilevel Inverter" *IEEE TRANSACTIONS ON POWER ELECTRONICS*, VOL. 15, NO. 4, JULY 2000

[19]. T.A. Meynard, H. Foch, "Multi-level Conversion: High Voltage Choppers and Voltage-source Inverters," *Proceedings of the IEEE Power Electronics Specialist Conference*, pages 397-403, 1992

[20]. F. Z. Peng, J. S. Lai, J. W. McKeever, J. VanCoevering, "A Multilevel Voltage-Source Inverter with Separate DC Sources for Static Var Generation," *IEEE Transactions on Industry Applications*, vol. 32, no. 5, Sept. 1996, pp. 1130-1138.

[21]. M. D. Manjrekar, T. A. Lipo, "A Generalized Structure of Multilevel Power Converter," *IEEE Conference on Power Electronics, Drives, and Energy Systems*, Australia, 1998, pp. 62-67.

[22]. Mr. G. Venkateswarlu, Dr.Psangameswar Raju P.GIRIPRASAD SINGH Analasis Of Photovoltaic Cell An Application Of A Level Shifted Cascaded Multilevel Inverter *International Journal of Engineering Research & Technology (IJERT)* Vol. 1 Issue 7, September – 2012

[23] R. Arulmurugan, N. Suthanthira Vanitha "Optimal Design of DC to DC Boost Converter with Closed Loop Control PID Mechanism for High Voltage Photovoltaic Application" *International Journal of Power Electronics and Drive System (IJPEDS)* Vol.2, No.4, December 2012, pp. 434~444