# DESIGN OF 32- BIT CARRY SELECT ADDER USING FULL SWING GATE DIFFUSION INPUT (FS- GDI) TECHNIQUE FOR DIGITAL SIGNAL PROCESSING APPLICATIONS.

<sup>1</sup>Vidisha Mathur ,<sup>2</sup> Latif Khan<sub>2</sub> <sup>1</sup>P.G. Scholar, <sup>2</sup>Asst.Professor <sup>1</sup> Electronics & Communication <sup>1</sup>Geetanjali Institute of Technical Studies, Udaipur, India.

**Abstract**-Designing of Low Power digital circuits is the challenging task in VLSI Industries. In this Paper we design low power & high speed 32 bit carry select adder using swing restoration buffer in gate diffusion input technique which is called full swing gat diffusion input techniques. Large number of carry select adder structures are available, we are designing carry select adder using Brent Kung adder and Binary to excess 1 converter instead of previous Ripple carry adder. This design drastically reducescarry propagation delay as well as power consumption of carry select adder. This design is prepared using Tanner EDA tools 15.1 and 180nm process technology.

# Index Terms- Full-SwingGDI, CSLA, Brent Kung Adder, Binary to Excess 1 Converter, Multiplexer

# 1. INTRODUCTION

Design of less occupied area, less delay, low power consumption and high speed adder logic systems are very important factors in the field of VLSI designing. Adder being one of the most popularly used components in digital circuitry as it performs an addition process and generates a carry and Sum. In conventional digital adder circuits, carry propagation delay being major hurdle that limits the speed of the addition process.

To resolve the problem of carry propagation delay, carry select adder was brought into existence that sorts the problem of propagation delay by generating partial sums and carry by taking into account both the carries viz. is Cin=0 and Cin=1, designed and assisted with Brent kung adder and binary to excess 1 converter to get better results. To further improve performance more in aspects of power consumption and delay, another technique introduced was Gate diffusion input technique which is even more improvised using swing restoration buffer called full swing gate diffusion input technique. Thus an efficient adder with less delay and less power consumption performing large no.of additions can be designed using above suggested method.

**1.1 Gate Diffusion Input Technique:-** Gate diffusion input technique works for low power and less area in VLSI digital circuits. This technique was found more efficient over all previously used techniques of CMOS, Transmission gate and Pass Transistor due to its better results in terms of power and delay. This technique uses very less number of transistors as compared to others and even design many complex functions using only 2 transistors.

#### Fig1:- Basic GDI Cell

This logic style undergoes a disadvadvantage of reduced output voltage swing. The reason behind this drawback is threshold drops i.e. the output is either high or low voltage or deviates from VDD or GND. This in turn results in poor performance and also increases short circuit power.

## Table 1: Different Logic Function Realization using GDI Cell.

| Ν | Р | G | OUT | Function |

|---|---|---|-----|----------|

| 0 | В | А | ĀB  | F1       |

| В | 1 | А | A+B          | F2  |

|---|---|---|--------------|-----|

| 1 | В | А | A+B          | OR  |

| В | 0 | А | AB           | AND |

| B | В | А | $A \oplus B$ | XOR |

| С | В | А | AB+AC        | MUX |

| 0 | 1 | А | -            | NOT |

# 2. Construction of CSLA Adder

A[31:28]B[31:28] A[15:12]B[15:12] A[11:8]B[11:8] A[7:4]B[7:4] A[3:0] B[3:0]

Fig 2: - Architecture of CSLA Adder

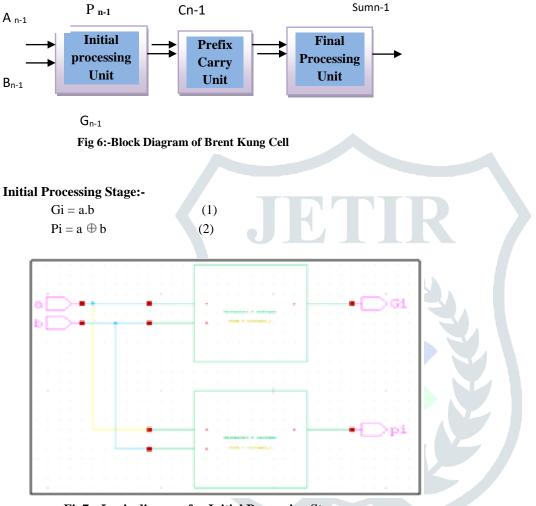

## 2.1 Brent Kung Adder

Brent kung adder is a type of Parallel prefix adder which is proposed and widely used over other prefix adders in spite of its long critical path and slow speed addition due to its capability of connecting gates in a way that minimize chip area.

The adder designed performs addition using Generation signal Gi and propagation signal Pi which finally evaluate sum through three stages :-

## Initial Processing Stage.

# Prefix Carry Stage.

## Final -Processing Stage.

*Initial-Processing Stage:* This is an initial stage which gives two important signals called generation signal and propagation signal Gi and Pi respectively.

*Prefix Carry Stage* :- This stage further simulate the two signals coming from previous stage using three cells namely black cell, gray cell and buffer which all combines to generate carry at the output.

Fig 3:- Prefix Carry Unit.

Black Cell:- This cell of the circuit is formed with a combination of one OR gate and two AND gate. As a result gives Gij and Pij as output.

Gray Cell:- This cell of the circuit is made using one OR and one AND gate resulting generation signal Grj as its output.

Buffer Cell:- This cell is simply used to amplify the strengths of the two signals.

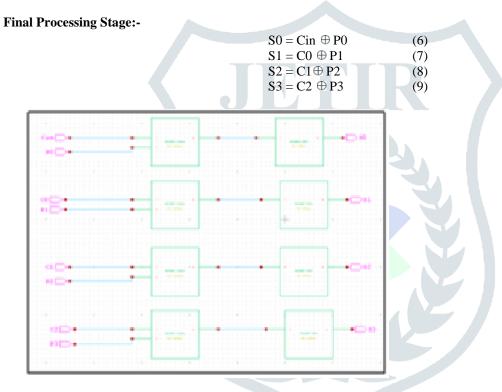

**Final Processing Stage:-** This is the final stage of Brent Kung adder that finally produces sum by performing an Ex-OR operation between carry of the previous stage and the propagation signal.

### 2.2. Binary to Excess 1 Converter

This is simply a digital device that adds an excess 1 to its input and gives an output accordingly. This feature of the device proved beneficial to reduce area and power consumption of the CSLA earlier designed using Ripple Carry adder by replacing the same with BEC.

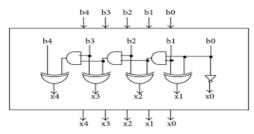

Fig 4:- Binary to Excess Converter

### TABLE 2:- Binary to Excess 1 Converter

| Binary Logic<br>B <sub>0</sub> B <sub>1</sub> B <sub>2</sub> B <sub>3</sub> | Excess-1 Logic<br>X <sub>0</sub> X <sub>1</sub> X <sub>2</sub> X <sub>3</sub> |

|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| 0000                                                                        | 0001                                                                          |

| 0001                                                                        | 0010                                                                          |

| 0010                                                                        | 0011                                                                          |

| 0011                                                                        | 0100                                                                          |

| 0100                                                                        | 0101                                                                          |

| 0101                                                                        | 0110                                                                          |

| 0110                                                                        | 0111                                                                          |

| 0111                                                                        | 1000                                                                          |

| 1000                                                                        | 1001                                                                          |

| 1001                                                                        | 1010                                                                          |

| 1010                                                                        | 1011                                                                          |

| 1011                                                                        | 1100                                                                          |

| 1100                                                                        | 1101                                                                          |

| 1101                                                                        | 1110                                                                          |

| 1110                                                                        | 1111                                                                          |

| 1111                                                                        | 0000                                                                          |

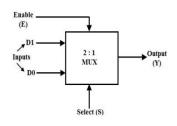

#### 2.3. Multiplexer

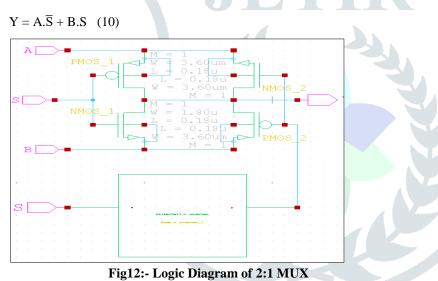

To design a 32 bit carry select adder, this paper uses 2:1 Multiplexer which has two input lines and one select line. Select line of each multiplexer receives previous carry at its input line in accordance to which desired Sum is displayed as output.

Fig 5:- 2X1 Multiplexer

Table 3:- Truth Table of 2:1 Mux

| Α | B | S | Y |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 1 |

# 3. Implementation of Carry Select Adder

This paper we have designed CSLA using Brent Kung Adder ,Binary to Excess-1 Converter and 2X1 Multiplexer. All components are designed and implemented by Full Swing Gate Diffusion Technique.

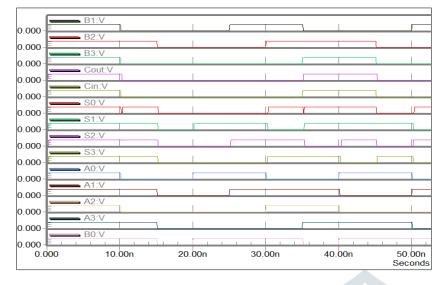

# 3.1. Designing of Brent Kung Adder:-

Fig7:- Logic diagram for Initial Processing Stage

Prefix Carry Stage:-

| Gij = Gik + (Pik.Gjk) | (3) |

|-----------------------|-----|

| Pij = Pik.Pjk         | (4) |

$$Grj = Gk + (Pk.Gkj)$$

(5)

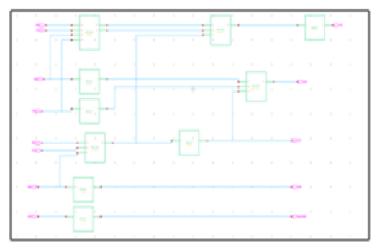

Fig 8:-Logic diagram of Prefix Carry Stage

Fig9:- Logic Diagram of Final Processing Stage

Fig10:-Logic Diagram of 4-Bit Brent Kung Adder

# 3.2. Binary to Excess 1 Converter:-

Fig11:- Logic Diagram of 4-Bit Binary to Excess 1 Converter

## 3.3. 2:1 Multiplexer:-

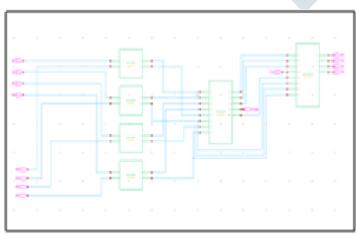

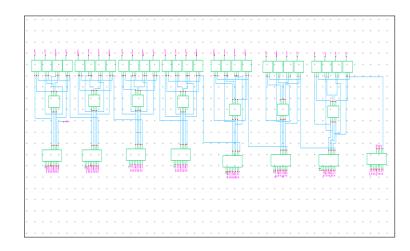

## 3.4. 32 Bit Carry Select Adder:-

Fig13:- Logic Diagram for 32- Bit CSLA

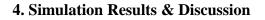

Fig 14: - Output Waveform of XOR Gate using FS- GDI

For inputs at a= 0 & b=1, o/p obtained y =1b/w 10ns- 20ns of max. up to 3.3 V.

For inputs at a=1 & b= 1, o/p y=0 b/0ns- 10ns and hence verified the truth table.

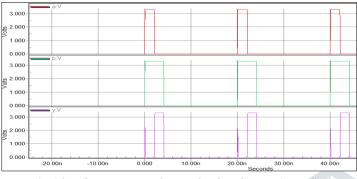

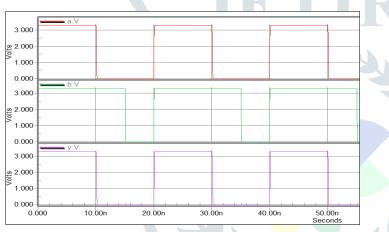

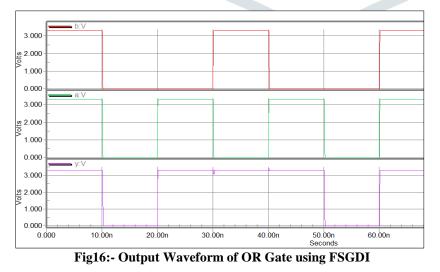

Fig15:-Output Waveform of AND Gate using FSGDI

- For inputs a = 1 & b = 1, o/p obtained is y = 1 b/w 0- 10ns up to max. of 3.3 V

- ➢ For inputs a=0 & b= 1, o/p obtained is y=0 b/w 30ns- 40ns up to max. of 3.3 V

- ➢ For inputs a= 1 & b=1, o/p y=1 obtained b/w 0ns- 10ns up to max. of 3.3 V

- For inputs a = 0 & b = 1, again o/p obtain is y = 1 b/w 10 ns 20 ns which verifies truth table

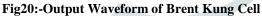

Fig21:- Output Waveform of Binary to Excess 1 Converter

- ➢ For input values B0= 1, B1= 0, B2 = 0, B3 = 0, the output X0= 0, X1= 1, X2= 0, X3= 0 seen & verified on time scale at 10ns.

- ➢ For input values B0= 1, B1= 1, B2= 1, B3=0, the output obtained X0 = 0, X1 = 0, X2 = 0 X3 = 1 seen & verified on time scale at 20ns.

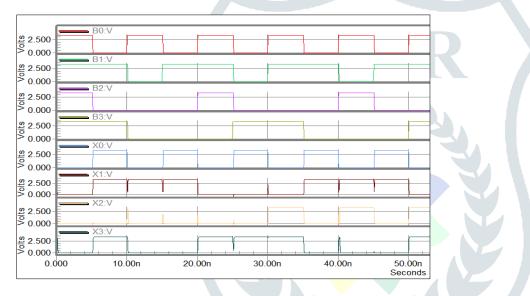

# Fig22:- Output Waveform of 2:1 Multiplexer

- ➤ For inputs A=0, B=1& S=0, the o/p y=0 on time scale b/w 5ns-10ns, hence verify the truth table.

- ➢ For inputs A=1,B=1 & S=1, the o/p obtained y=1 on time scale b/w 0ns-5ns & hence verified.

|                                                                 | <ul> <li>S6:V</li> </ul> |        |          |        |                   |        |

|-----------------------------------------------------------------|--------------------------|--------|----------|--------|-------------------|--------|

| 0.000                                                           | S7:V                     |        | ( ) I    |        |                   | D C    |

| 0.000                                                           | - S8:V                   |        | i/       |        |                   |        |

| 0.000                                                           | - 59:V                   | - I    |          | 1      |                   |        |

| 0.000                                                           | \$10:V                   | U.     |          | . /    |                   |        |

| 0.000                                                           | \$11:V                   |        |          |        | ~ ~               |        |

| 0.000                                                           | S12.V                    |        | V        |        | 1                 | (      |

| 0.000                                                           | \$12.V                   |        |          |        | × 1               |        |

| 0.000                                                           | S14:V                    | 6      |          |        | _                 | /      |

| 0.000                                                           |                          |        | <i>(</i> |        |                   | n (    |

| 0.000                                                           | 515:V                    |        | · · · ·  |        |                   |        |

| 0.000                                                           | - S0:V                   |        |          |        |                   |        |

| 0.000                                                           | ■ S1:V                   |        |          |        |                   |        |

| 0.000                                                           | S2:V                     |        |          |        |                   |        |

| 0.000                                                           | <b>\$3:V</b>             |        |          |        |                   |        |

|                                                                 | - S4:V                   |        |          |        |                   |        |

|                                                                 |                          |        |          |        |                   |        |

| 0.000                                                           | 55:V                     |        |          |        |                   |        |

| 0.000                                                           | 10.00n                   | 20.00n | 30.00n   | 40.00n | 50.00n<br>Seconds | 60.00n |

| 3.000 -<br>2.500 -<br>2.000 -<br>1.500 -<br>1.000 -             | 10.00n                   | 20.00n | 30.00n   | 40.000 | 50.00n<br>Seconds | 60.00n |

| 3.000-<br>2.500-<br>1.500-                                      | 10.00n                   | 20.00n | 30.bon   | 40.000 | 50.00n<br>Seconds | eo.bon |

| 3.000 -<br>2.500 -<br>2.500 -<br>1.500 -<br>500.0m -<br>3.000 - | 10.00n                   | 20.000 | 30 bon   | 40.bon | So Don<br>Seconds | eo bon |

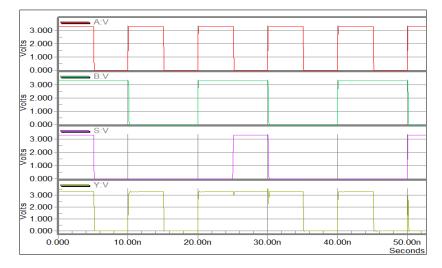

## Fig23:- Output waveform of 32-bit Carry Select Adder

The o/p Sum(S0-S31) of 32-bit carry select adder is checked & verified at time scale of 60ns for input values of A(A0-A31), B(B0-B31), cout=1 & cin = 0.

# 5. Graphical Comparisons in terms of Delay & Power Consumption.

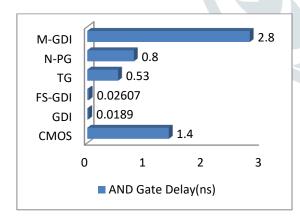

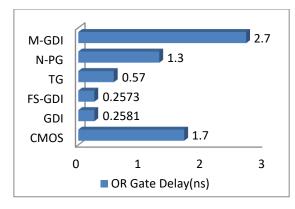

## 5.1 Delay Comparison:-

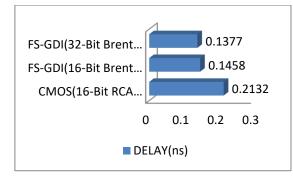

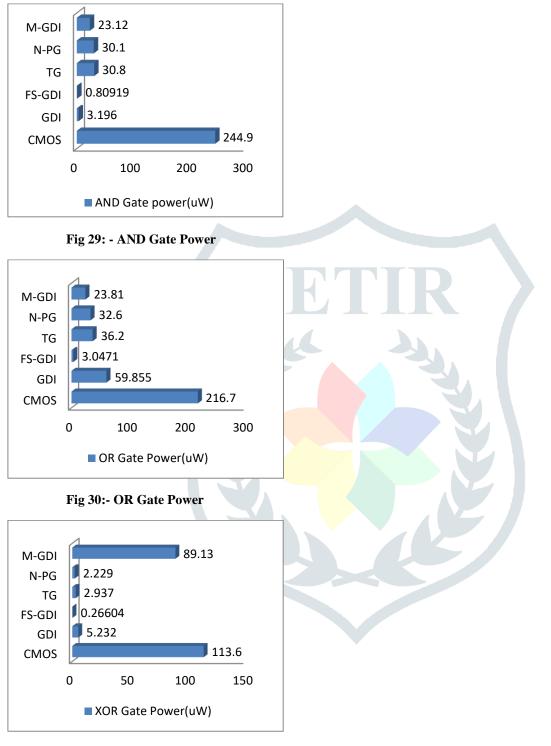

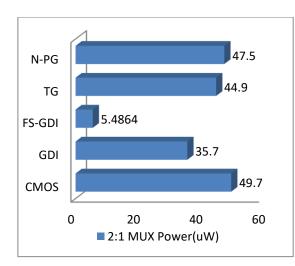

Firstly, Average Delay for AND, OR & XOR Gates were calculated using Trans Delay Measure of Spice Command available as tools in S- Edit of Tanner EDA Tools in 15.1 & 180nm technology.

Further, Avg. delays of these three logic gates are than compared with the delays obtained for these gates designed using various other logics as shown below: -

Fig 24: - AND Gate Delay

Fig 25: - OR Gate Delay

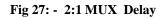

Fig 28: - 32-bit CSLA Delay

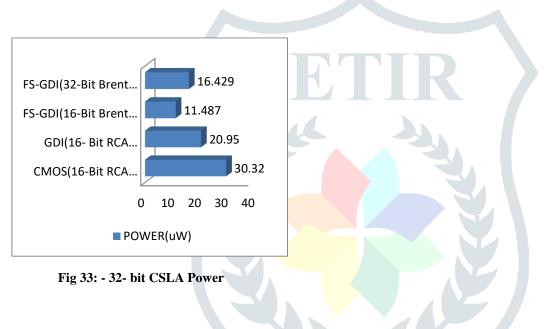

# 5.1 Power Consumption Comparison:-

Power is calculated using ".POWER "formula by writing in T- Spice. The power of these gates are than compared with the powers of the Gates designed in other logics are shown below:-

Fig 31: - XOR Gate Power

`Fig 32: - 2:1 MUX Power

# 6.Conclusion:-

In this design of 32 bit Carry Select Adder with a special Brent Kung Adder developed using Full Swing Gate Diffusion Technique (GDI). The proposed design is simulated using Tanner EDA Tool 15.1 and designed in 180nm technology, the obtained results and comparison gave fantastic improvement in delay and Power consumption over earlier 32-bit CSLA. In FSGDI based 32-bit CSLA has a propagation delay of around 0.1377nsec which is quite less compare to previous designed techniques .Likewise, Power consumed by 32-bit CSLA designed using FS GDI is only 16.429uW.

# 7.References:-

1. Omnia Al. Badry, M. A. Abdelghany 2018 International Conference on Innovative Trends in Computer Engineering (ITCE 2018), Aswan University, Egypt for Low Power 1-Bit Full Adder Using Full-Swing Gate Diffusion Input Technique.

2.Jamuna, Renugadevi, Saranya, Sharmila, Suruthipriya, for Area Efficient Carry Select Adder Using Modified Brent Kung Adder[2016].

3.Pappu P. Potdukhe, Vishal D. Jaiswal, for Review of Carry Select Adder by using Brent Kung Adder.[2015].

4. Mahmoud Aymen Ahmed, M. A. Abdelghany, 2018 International Conference on Innovative Trends in Computer Engineering (ITCE 2018), Aswan University,Egypt,

for Low Power 4-Bit Arithmetic Logic Unit Using Full-Swing GDI Technique.

5. M. Soundharya, R. Arunkumar, 2015 Online International Conference on Green Engineering and Technologies, forGDI Based Area Delay Power Efficient Carry Select Adder.

6. Jubal Saji and Shoaib Kamal, 2015 1st International Conference on Next Generation

Computing Technologies (NGCT-2015) Dehradun, India, 4-5 September 2015, for A Low Power Variable Sized CSLA Implementation using GDI Logic In 45nm SOI Technology.

7. P. Nithin, N. Udaya Kumar and K. Bala Sindhuri, Indian Journal of Science and Technology, Vol 9(44), DOI: 10.17485/ijst/2016/v9i44/101948, November 2016, Implementation of 32-Bit Carry Select Adder using Brent-Kung Adder.

8. BalaSindhuri K, PadmaVasavi K, Santi Prabha I, Udaya Kumar N. VLSI architecture for linear Carry Select Adder with zero finding. 6th International Advanced Cloud Computing Conference IACC; 2016.

9. Usha, M. Rajendiran, A. Kavitha, for "Low Power Area Efficient ALU with Low Power Full Adder" IEEE International Conference on Computing for Sustainable Global Development (INDIACom), pp. 1500-1505, 2016.

10. Korraravikumar, AL Reddy, M.Sadanandam, Santhoshkumar.A and M.Raju," Design of 2T XOR Gate Based Full Adder Using GDI Technique", International Conference on Innovative Mechanisms for Industry Applications(ICIMIA 2017),2017