# A NOVEL REVERSIBLE DECODER FOR DESIGN AND SYNTHESIS OF COMBINATIONAL CIRCUITS

# D.Neelima<sup>1</sup>, S.Ali Asgar<sup>2</sup>, Dr.V.Thrimurthulu<sup>3</sup>,

<sup>1</sup>II M.Tech (VLSISD), Dept. of ECE, Chadalawada Ramanamma Engineering College, Tirupati. <sup>2</sup> Assistant professor, Dept. of ECE, Chadalawada Ramanamma Engineering College, Tirupati. <sup>3</sup> Professor & Head, Dept. of ECE, Chadalawada Ramanamma Engineering College, Tirupati.

Abstract: - Reversible Logic has become one of the most promising research areas in recent decades and its applications in various technologies; As a CMOS with low consumption, nanotechnology and optical processing. The main purpose of designing reversible logic is to reduce quantum cost, depth of circuits, and number of waste products. The purpose of this document is to provide a framework, understanding, and review of reversible doors. In this document, various logical gates and their applicability to logical design are discussed. In addition, a brief overview of the comparison between reversible circuits based on various parameters is presented. The combination of decoders, comparators, full adders and multiplexers is designed using Fredkin Gate, CNT and GatePres, which offer better quantum costs than other reversible gates. Reversible logic circuits are designed and implemented using the VERILOG code, and the simulation results are obtained in Simulux ISE version 14.1.

Index Terms: Multiplexers, Decoders, Adders, Fredkin gate, Comparators

# **1. INTRODUCTION**

In current VLSI technology, power consumption has become an important consideration. Using a reversible decoder to design combination circuits reduces the power consumption optimally compared to conventional decoder based combination circuits. Reversible Logic finds its own application in quantum computing, nanotechnology, optical computing, computer graphics and low power VLSI. Ralph Launder [1] stated that the thermal dissipation of the circuits is not due to the process involved in the operation, but to the bits that were cleared during the process. He presented that the loss of a single bit in the circuit can be attributed to the smallest heat in the calculation, which is equivalent to 2 jt of KTLN, where K is the Boltzmann constant and T is the temperature. Although the amount of heat spread in simple circuits is small, it becomes larger in complex circuits, which also implies propagation delay. Later, in 1973, C. H. Bennett [2] explained that the power dissipation caused by the bit loss can be overcome if each of the calculations in the circuit is reversed. Quantum networks are designed by quantum logic gates. The KTln2 joules energy distribution will not occur if each gate has a unified operation, reversing the calculation. Therefore, there is no need to clear bits for reversible computations. The amount of heat spread over the system is directly related to the number of bits that are cleared or lost during the calculation.

## 2. CONCEPT

The use of reversible gates in reversible logic involves the same number of inputs and p outputs, that is, one to one mapping between input vectors and output output vectors. They can also run in the backward direction. There are some limitations to be considered when designing circuits based on reversible logic: (i) fan outing is not allowed in reversible logic; (ii) feedback is not allowed in reversible logic. In reversible logic using P outputs we can get complete knowledge about the inputs. Reversible logic saves information. Some measures, such as waste p outputs, number of gates, quantum cost, and fixed inputs, are used to measure the performance of reversible circuits. Waste p outputs are additional p outputs that help equalize inputs and p outputs to maintain reversibility. It leaves them alone with no activity. The number of gates required to implement the gate. This is just the number of reversible gates ( $1 \times 1$  or  $2 \times 2$ ) needed to build the circuit. Delays are a major cost measure. Reversible circuit design can be modeled as a series of separate time slices, and depth is the summary of total time slices. In digital electronics, the binary decoder is a combination logic circuit that converts the binary integer value into the corresponding output output pattern. Various proposals have been devoted to the design of combination and sequential circuits in the ongoing research. In this paper, we suggest the design of different combination circuits, binary comparator, full adder, full subtractor, and multiplexer circuits using reversible decoder at excellent quantum cost.

# **3.. REVERSIBLE LOGIC GATES**

The basic Reversible Logic Gates present in the literature are briefed below. The gates that are suitable for the design with optimum quantum cost can be selected.

3.1. *NOT GATE:* Not Gate is simple Reversible logic gate. It is a  $1 \times 1$  reversible logic gate with quantum cost zero. As shown in Figure 1, the gate gate converts the input complement to the output. This is the basic primitive gate that may be involved in the construction of the reversible logic gate Importance in determining the quantum cost of a designed reversible logic gate.

Fig. 1 NOT Gate and its Truth Table

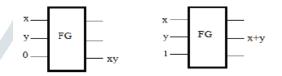

#### 3.2. FEYNMAN GATE (FG):

The Feynman Gate is a  $2 \times 2$  reversible gate, as shown in Figure 2. Feynman Gate is also known as Sinot Gate, which means restricted note gate. Feynman Gate is used to duplicate the required p output as fan-out is not allowed in reversible logic gates. The quantum cost of FG is 1. It is also a primitive gate because of its importance in determining the quantumcost

Fig. 2 Feynman Gate and its Truth Table

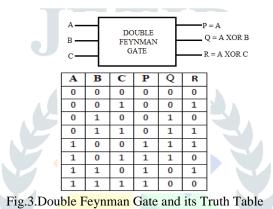

### 3.3. DOUBLE FEYNMAN GATE (DFG):

The double Feynman Gate is a  $3 \times 3$  reversible gate. The p outputs are defined as shown in Figure 3 below. Quantum cost of DFG 2. This gate can also be used to duplicate p outputs.

#### 3.4. TOFFOLI GATE

(TG): Toffoli Gate is 3×3 reversible gate. The outputs are defined as shown in the below figure 4. The Quantum Cost of TG is 4.

| A<br>B<br>C |       | TOFFOLI<br>GATE |          |     |   | P = A $Q = B$ $R = AB  XOR  C$ |   |  |  |

|-------------|-------|-----------------|----------|-----|---|--------------------------------|---|--|--|

|             | Α     | B               | С        | Р   | Q | R                              |   |  |  |

|             | 0     | 0               | 0        | 0   | 0 | 0                              |   |  |  |

|             | 0     | 0               | 1        | 0   | 0 | 1                              |   |  |  |

|             | 0     | 1               | 0        | 0   | 1 | 0                              |   |  |  |

|             | 0     | 1               | 1        | 0   | 1 | 1                              |   |  |  |

|             | 1     | 0               | 0        | 1   | 0 | 0                              |   |  |  |

|             | 1     | 0               | 1        | 1   | 0 | 1                              |   |  |  |

|             | 1     | 1               | 0        | 1   | 1 | 1                              |   |  |  |

|             | 1     | 1               | 1        | 1   | 1 | 0                              |   |  |  |

|             | . 4 T |                 | <u> </u> | 1 . |   | 1 70 1                         | 1 |  |  |

Fig.4 Toffoli Gate and its Truth Table

## 5. FREDKIN GATE (FDG): Fredkin Gate is a 3×3

reversible gate. The outputs are defined as shown in the below figure4. The Quantum Cost of FDG is 5. This paper mainly surrounds around Fredkin gate.

| Α | В | С | Р | Q | R |

|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 0 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 | 1 |

| 1 | 0 | 0 | 1 | 0 | 0 |

| 1 | 0 | 1 | 1 | 1 | 0 |

| 1 | 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 | 1 |

Fig.5 Fredkin Gate and its Truth Table

## 4. BASIC GATES USING REVERSIBLE GATES

AND & OR gates should be designed with reversible gates according to our circuit requirements. We used the Fredkin gate to design the AND, or gates, as shown in Figure 6. Fredkin Gate is important because it is optimistic AND, or quantum cost effective performance for designing gates.

Fig.6 AND Gate using fredkin and OR Gate using fredkin

#### **V.SIMULATION RESULTS**

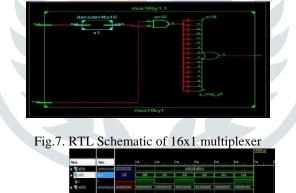

To design a multiplexer using reversible decoder, reversible 2 input AND gates, 2 input OR gates are required. The 2 input AND Gate and OR gate are designed using Fredkin gate. By using these designed gates we can improve those gates to the required number of input gate. Each output line from decoder is driven to 2 input AND gate along with multiplexer input. The outputs of all AND gates are made to drive to that particular input OR gate. The input binary integer values act as the selection lines. Similarly by using  $4 \times 16$  decoder a  $16 \times 1$  multiplexer is designed. The RTL Schematic and the simulated outputs of  $16 \times 1$  multiplexer are shown in figure.

Fig.8.simulated output of 16x1 multiplexer

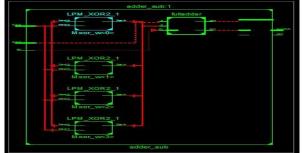

### a.ADD – SUB:

To design 4-bit full adder/subtractor circuit four full adders are required. The Cin input drives the first full adder. If Cin is given with low input 4-bit addition is performed and if Cin is given with high input the 4-bit subtraction in the form of 1's complement addition is performed

| Name        | Value | 1717 1773                                                                                                      | lus  | 2us      | 3us      | 4us  | 5us  | ឥរន | a na an | 7us   8 |

|-------------|-------|----------------------------------------------------------------------------------------------------------------|------|----------|----------|------|------|-----|---------|---------|

| 🕨 🕌 a[Búlj  | 1110  | m                                                                                                              | 0101 | <u> </u> | 1111     |      |      | 180 |         |         |

| ▶ 🕌 bβ#j    | 0101  | un                                                                                                             |      | 1001     |          |      | 0101 |     |         |         |

| g in        | 0     | _                                                                                                              |      |          |          |      |      | L   |         |         |

| 🕨 🕌 sum[30] | 0011  | XOX                                                                                                            | 1110 | 1000     | 0110     | 1010 | 1001 | C   | 0011    |         |

| a cout      | 1     | the second s |      |          | <b>[</b> | 1    |      |     |         |         |

| 🕨 🙀 w[35]   | 0101  | XOX                                                                                                            | 1    | 001      | 0110     | . 1  | 010  |     | 0101    |         |

| lig wi      | 0     |                                                                                                                |      |          | 1        |      |      |     |         |         |

| w2          | D     | 5                                                                                                              |      |          |          |      |      |     |         |         |

| l∦ w3       | 1     |                                                                                                                |      |          |          |      |      |     |         |         |

Fig.9. Simulated output of add-sub

Fig.10. RTL Schematic of add-sub

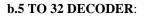

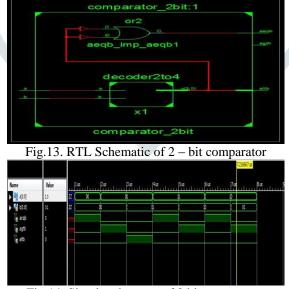

## C.2 – BIT COMPARATOR:

The output lines g, l, e represents Greater, Lesser, Equal respectively. The a, b lines represents the inputs. If a<br/>b then 'l' output becomes high. If a>b then 'g output ' becomes high. If a=b then output e becomes high.

Fig.14. Simulated output of 2 bit comparator

## VI. COMPARATIVE STUDY

The combinational circuits designed using reversible decoder are analyzed in terms of Quantum cost .

| Parameter   | Quantum Cost |          |  |  |  |

|-------------|--------------|----------|--|--|--|

| Parameter   | Existing     | Proposed |  |  |  |

| 5 to 32     | 455          | 454      |  |  |  |

| decoder     | 155          | 151      |  |  |  |

| 2 bit       | 140          | 126      |  |  |  |

| comparator  | 140          | 136      |  |  |  |

| 16x1 MUX    | 150          | 146      |  |  |  |

| 4-bit       |              |          |  |  |  |

| Adder/Subtr | 264          | 248      |  |  |  |

| actor       |              |          |  |  |  |

#### VII. CONCLUSION

In this paper, different combination circuits such as adder/subtractor, comparator, multiplexer, and decoder are compared. These circuits are designed for low quantum cost. The proposed method can be generalized to design the decoder circuit. The idea of duplicating the single output output to the output output required to overcome the fan-limit constraint in reversible logic circuits is used. This method of designing combination circuits enables many digital circuits to be implemented with great performance at minimum quantum cost.

#### REFERENCES

[1] R. Landauer, "Irreversibility and Heat Generation in the Computational Process", IBM Journal of Research and Development, 5, pp. 183-191,1961.

[2] C.H. Bennett, "Logical Reversibility of Computation", IBM J.Research and Development, pp. 525-532, November 1973.

[3] C H Bennett, "Notes on the History of Reversible Computation", IBM Journal of Research and Development, vol. 32, pp. 16-23, 1998.

[4] R. Feynman,"quantum mechanical computers:, Optic News, vol. 11,pp 11-20, 1985.

[5] William C. Athas, Lars "J", Svensson, Jeffrey G. koller, Nestoras Tzartzanis, and Eric Ying – Chin Chou, "Low-power Digital Systems based on Adiabatic-Switching principle", IEEE Transactions on VLSI systems, Vol. 2, No. 4, December 1994.

[6] A. Peres, "Reversible logic and quantum computers", phys.rev.A,Gen.Phys., vol. 32, no. 6, pp. 32663276, Dec. 1985.

[7] H.G Rangaraju, U. Venugopal, K.N. Muralidhara, K. B. Raja,"Lowpower reversible parallel binary adder/subtractor" arXiv.org/1009.6218,2010.

[8] J.M. Rabaey and M. Pedram, "Low Power Design Methodologies," Kluwer Academic Publisher, 1997.

[9] T. Toffoli., "Reversible Computing", Tech memo MIT/LCS/TM-151, MIT Lab for Computer Science 1980.

[10] ] E. Fredkin and T. Toffoli, "Conservative logic," Int'l J.Theoretical Physics, Vol. 21, pp.219–253, 1982.

[11] 8]Y. Syamala, and A. V. N. Tilak, "Reversible Arithmetic Logic Unit", Electronics Computer Technology (ICECT), 2011 3rd International, vol.5, pp.207-211,07 july 2011.

[12] Thapliyal H, Ranganathan N.," Design of Reversible Latches Optimized for Quantum Cost, Delay and Garbage Outputs" Centre for VLSI and Embedded.

[13] V.Rajmohan, V.Ranganathan,"Design of counter using reversible logic" 978-1-4244-8679-3/11/\$26.00 ©2011 IEEE.

[14] Vivek V. Shende, Aditya K. Prasad, Igor L. Markov, and John P. Hayes," Synthesis of Reversible Logic Circuits", IEEE Transaction on computer-aided design of integrated circuits and systems, vol. 22, No. 6, June 2003.