# Performance Improvement in Ultra-Low Power 18-Transistor Single-Phase Clocked Flip-Flop in CMOS

<sup>1</sup>Ayushi Nagar, <sup>2</sup>Prof. Rahul Shrivastava

<sup>1</sup>M.Tech scholar, <sup>2</sup>Assistant Professor <sup>1&2</sup>Department of Electronics and Communication, <sup>1&2</sup>Sagar Institute of Science and Technology, Bhopal, India.

*Abstract*: CMOS is an innovation for developing coordinated circuits. CMOS innovation is utilized in chip, microcontrollers, static Smash, and other computerized rationale circuits. The most fundamental sequential circuit type that we will ponder is known as the Flip-Flop. True single-phase clock (TSPC) method of reasoning has found wide use in advanced plan. A transmission gate based FF (TGFF) design is used most widely, due to its fully static operation, robust voltage scaling, and none data contention. However, a major drawback of TGFF is the excessive working load to the clock signal, which leads to considerably dynamic power even in low or zero switching activity. This paper is presenting an efficient design of true single phase clocking based trusted storage in CMOS.

IndexTerms -TSPC, VLSI, Flip-Flop, Clock, RAM, ROM, SRAM, DRAM.

# I. INTRODUCTION

Two vital attributes of CMOS gadgets are high clamor invulnerability and low static power utilization. Since one transistor of the match is constantly off, the arrangement blend draws huge power just quickly amid turning among on and off states. Subsequently, CMOS gadgets don't create as much waste warmth as different types of rationale, for instance transistor–transistor rationale (TTL) or N-type metal-oxide-semiconductor rationale (NMOS) rationale, which ordinarily make them stand current notwithstanding when not evolving state. CMOS additionally permits a high thickness of rationale works on a chip. It was fundamentally therefore that CMOS turned into the most utilized innovation to be executed in very-large-scale integration (VLSI) chips.

The expression "metal- oxide- semiconductor" is a reference to the physical structure of certain field-effect transistors, having a metal door anode put over an oxide separator, which thus is over a semiconductor material. Aluminum was once utilized yet now the material is polysilicon. Other metal doors have made a rebound with the appearance of high- $\kappa$  dielectric materials in the CMOS procedure, as reported by IBM and Intel for the 45 nanometer hub and littler sizes.

"CMOS" alludes to both a specific style of advanced hardware plan and the group of procedures used to execute that hardware on coordinated circuits (chips). CMOS hardware disperses less power than rationale families with resistive burdens. Since this preferred standpoint has expanded and developed more essential, CMOS procedures and variations have come to overwhelm, accordingly most by far of present day coordinated circuit fabricating is on CMOS forms.

CMOS circuits utilize a blend of p-sort and n-type metal- oxide- semiconductor field-effect transistor (MOSFETs) to execute rationale doors and other advanced circuits. Despite the fact that CMOS rationale can be executed with discrete gadgets for showings, business CMOS items are incorporated circuits made out of up to billions of transistors of the two sorts, on a rectangular bit of silicon of somewhere in the range of 10 and 400 mm2.CMOS dependably utilizes all improvement mode MOSFETs.

True Single Phase Clock (TSPC) is a general unique flip-flop that works at fast and expends low power. The capacity of a clocked storage component is to catch the data at a specific minute in time and protect it as long as it is required by the advanced framework. Having said as much, it is unimaginable to expect to characterize a storage component without characterizing its relationship to a clocking instrument in a computerized framework, which is utilized to decide discrete time occasions. This definition is general and ought to incorporate different methods for executing an advanced framework. All the more especially the component that decides time in a synchronous framework is the clock.

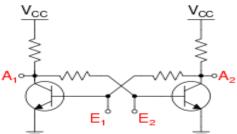

Figure 1: A traditional (simple) flip-flop circuit based on bipolar junction transistors

A clock signal is delivered by a clock generator. Albeit increasingly complex game plans are utilized, the most widely recognized clock signal is as a square wave with a half obligation cycle, generally with a fixed, consistent recurrence. Circuits utilizing the clock signal for synchronization may end up dynamic at either the rising edge, falling edge, or, on account of twofold information rate, both in the rising and in the falling edges of the clock cycle.

#### © 2019 JETIR June 2019, Volume 6, Issue 6

#### www.jetir.org (ISSN-2349-5162)

Clock signals are normally stacked with the best fanout and work at the most noteworthy velocities of any signal inside the synchronous framework. Since the information signals are given a transient reference by the clock signals, the clock waveforms must be especially perfect and sharp. Moreover, these clock signals are especially influenced by innovation scaling (see Moore's law), in that long worldwide interconnect lines become essentially progressively resistive as line measurements are diminished. This expanded line opposition is one of the essential purposes behind the expanding importance of clock appropriation on synchronous execution. At long last, the control of any distinctions and vulnerability in the entry times of the clock signals can seriously restrain the greatest execution of the whole framework and make cataclysmic race conditions in which an inaccurate information signal may hook inside a register.

Most synchronous advanced frameworks comprise of fell banks of sequential registers with combinational rationale between each arrangement of registers. The practical necessities of the computerized framework are fulfilled by the rationale stages. Every rationale arrange presents defer that influences timing execution, and the planning execution of the computerized structure can be assessed with respect to the planning necessities by a planning examination. Regularly extraordinary thought must be made to meet the planning prerequisites. For instance, the worldwide execution and nearby planning prerequisites might be fulfilled by the watchful addition of pipeline registers into similarly divided time windows to fulfill basic most pessimistic scenario timing limitations. The best possible plan of the clock dispersion arrange guarantees that basic planning necessities are fulfilled and that no race conditions exist.

# II. TRUE SINGLE PHASE CLOCK ARCHITECHTURE

Most integrated circuits (ICs) of adequate unpredictability utilize a clock signal with the end goal to synchronize diverse parts of the circuit, cycling at a rate slower than the most pessimistic scenario inside engendering delays. At times, in excess of one clock cycle is required to play out an anticipated activity. As ICs turn out to be more mind boggling, the issue of providing exact and synchronized clocks to every one of the circuits turns out to be progressively troublesome. The transcendent case of such complex chips is the microchip, the focal part of present day PCs, which depends on a clock from a precious stone oscillator. The main special cases are non concurrent circuits, for example, offbeat CPUs.

A clock signal may likewise be gated, that is, joined with a controlling signal that empowers or handicaps the clock signal for a specific piece of a circuit. This method is frequently used to spare power by effectively closing down bits of an advanced circuit when they are not being used, but rather includes some significant pitfalls of expanded intricacy in timing investigation.

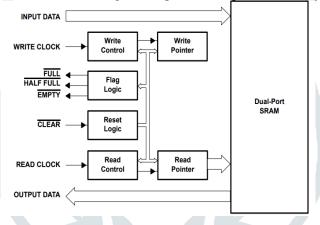

Figure 2: Block diagram of FIFO with storage

In figure 2, a long fall-through time in long FIFOs, the engineering should never again move the information words through all memory areas. The issue is fathomed by a roundabout memory with two pointers. In a roundabout FIFO idea, the memory address of the approaching information is in the compose pointer. The location of the main information word in the FIFO that will be perused out is in the perused pointer. After reset, the two pointers demonstrate a similar memory area. After each compose task, the compose pointer is set to the following memory area. The perusing of an information word sets the read pointer to the following information word that will be perused out. The read pointer continually pursues the compose pointer. At the point when the read pointer comes to the compose pointer, the FIFO is vacant. In the event that the compose pointer gets up to speed with the read pointer.

## III. PROPOSED METHODOLOGY

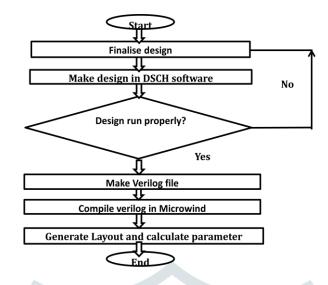

## Algorithm-

Step 1- Firstly make design in DSCH software using available component then make connection between them as per requirement.

Step 2- Now press run simulation and see output in terms of LED glow or not, if input and clock is on and led glow then designed circuit give proper output otherwise there are some errors in circuit.

Step 3- Now save this design and make verilog file, then a verilog file will be generated automatic.

Step 4- Open Microwind software and compile verilog file. Then generate CMOS layout. Now calculate parameters and compare result.

This work proposes 18-transistor SPC (18TSPC), a SPC FF with only 18 transistors (the lowest reported for a fully static contention-free SPC FF) with a novel master-slave Fig. 3. Simulation results show TCFF internal node voltages at (a) VDD = 1.2 V and (b) VDD = 0.6 V when D rising at CK = 0 [15]. topology With a simplified topology, it delivers a 20% reduction in cell area compared to TGFF. Unlike SoA designs, 18TSPC meets all ultra-low power FF design requirements. It has been implemented in 65-nm CMOS along with a TGFF. This proves EDA compatibility and demonstrates circuit and system-level benefits. The design was first simulated then experimentally validated at 0.7 V, 25 °C, at various data activity rate ( $\alpha$ ), showing

## © 2019 JETIR June 2019, Volume 6, Issue 6

#### www.jetir.org (ISSN-2349-5162)

that the proposed 18TSPC achieves reductions of 68% and 73% in overall ( $P\alpha=10\%$ ) and clock dynamic power ( $P\alpha=0\%$ ), respectively, and 27% lower leakage compared to TGFF. Furthermore, unlike TCFF, the measurements indicate superior 18TSPC in performance.

#### Figure 3: Flow Chart

# **IV. SIMULATION AND RESULT**

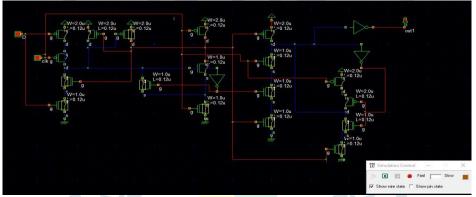

Figure 4: Proposed 18-transistor single-phase clocked (TSPCFF)

Figure 4 showing design of transistor single-phase clocked. AND gate, PMOS and CMOS component are using to design this circuit. To check result, when clk=1 d=1 then output=1

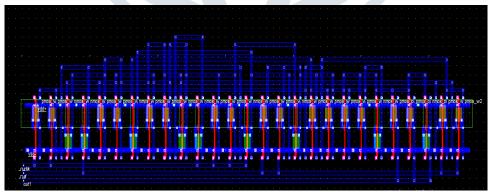

Figure 5: Layout of 18-TSPCFF

Figure 5 presentation CMOS layout design of TGFF, it includes various metal, PMOS, NMOS and contact points.

| Sr<br>No. | Parameters          | Value   |

|-----------|---------------------|---------|

| 1         | Area                | 374.0µm |

| 2         | Power               | 7.749µW |

| 3         | Delay               | 7ns     |

| 4         | Power Delay Product | 542.43  |

| 5         | Rise time           | 0.025ns |

| 6         | Fall time           | 0.025ns |

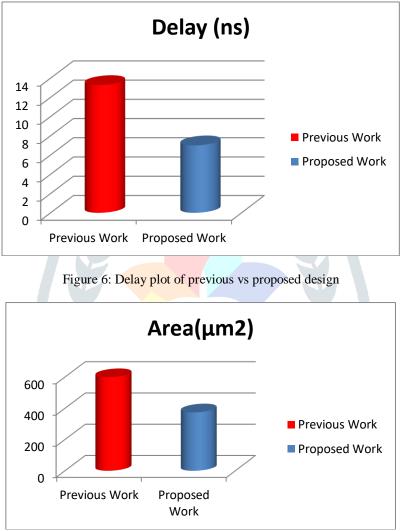

Figure 7: Area plot of previous vs proposed design

Therefore to see all simulated result and parameter values, it is observed that proposed design performance is better than previous designs.

# **V. CONCLUSION**

This paper proposed 18TSPC, a fully static and contention free SPC FF with the lowest reported number of transistors(18), demonstrating a significant cell area reduction with respect to the conventional TGFF. Although a performance penalty is observed, thanks to the low-power characteristic of the proposed design, 18TSPC achieves more. A brief summary of the proposed 18TSPC and comparison with prior works is presented. Therefore proposed 18TSPC has better power characteristics than the previous.

# REFERENCE

1. Y. Cai, A. Savanth, P. Prabhat, J. Myers, A. S. Weddell and T. J. Kazmierski, "Ultra-Low Power 18-Transistor Fully Static Contention-Free Single-Phase Clocked Flip-Flop in 65-nm CMOS," in *IEEE Journal of Solid-State Circuits*, vol. 54, no. 2, pp. 550-559, Feb. 2019.

#### © 2019 JETIR June 2019, Volume 6, Issue 6

- W. Wang, S. Jia, Z. Wang, T. Pan and Y. Wang, "Low Voltage Dual-Modulus Frequency Divider Based on Extended True Single-Phase Clock Logic," 2018 IEEE International Conference on Electron Devices and Solid State Circuits (EDSSC), Shenzhen, 2018, pp. 1-2.

- 3. J. Shaikh and H. Rahaman, "High speed and low power preset-able modified TSPC D flip-flop design and performance comparison with TSPC D flip-flop," *2018 International Symposium on Devices, Circuits and Systems (ISDCS)*, Howrah, 2018, pp. 1-4.

- P. Xu, C. Gimeno and D. Bol, "Optimizing TSPC frequency dividers for always-on low-frequency applications in 28nm FDSOI CMOS," 2017 IEEE SOI-3D-Subthreshold Microelectronics Technology Unified Conference (S3S), Burlingame, CA, 2017, pp. 1-2.

- 5. F. Stas and D. Bol, "A 0.4V 0.08fJ/cycle retentive True-Single-Phase-Clock 18T Flip-Flop in 28nm FDSOI CMOS," 2017 IEEE International Symposium on Circuits and Systems (ISCAS), Baltimore, MD, 2017, pp. 1-4.

- 6. J. Lin, M. Sheu, Y. Hwang, C. Wong and M. Tsai, "Low-Power 19-Transistor True Single-Phase Clocking Flip-Flop Design Based on Logic Structure Reduction Schemes," in *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 25, no. 11, pp. 3033-3044, Nov. 2017.

- H. Ashwini, S. Rohith and K. A. Sunitha, "Implementation of high speed and low power 5T-TSPC D flip-flop and its application," 2016 International Conference on Communication and Signal Processing (ICCSP), Melmaruvathur, 2016, pp. 0275-0279.

- S. Jia, Z. Wang, Z. Li and Y. Wang, "A novel low-power and high-speed dual-modulus prescaler based on extended true single-phase clock logic," 2016 IEEE International Symposium on Circuits and Systems (ISCAS), Montreal, QC, 2016, pp. 2751-2754.

- 9. S. S. Varma, A. Sharma and B. Anand, "An efficient methodology to characterize the TSPC flip flop setup time for static timing analysis," 2016 13th International Conference on Synthesis, Modeling, Analysis and Simulation Methods and Applications to Circuit Design (SMACD), Lisbon, 2016, pp. 1-4.

- 10. S. Jia, S. Yan, Y. Wang and G. Zhang, "Design of low-power high-speed divide-by-2/3 prescalers with improved true single-phase clock scheme," 2014 Asia-Pacific Microwave Conference, Sendai, Japan, 2014, pp. 241-243.

- 11. X. Tang, J. Zhang, P. Gaillardon and G. De Micheli, "TSPC Flip-Flop circuit design with three-independent-gate silicon nanowire FETs," 2014 IEEE International Symposium on Circuits and Systems (ISCAS), Melbourne VIC, 2014, pp. 1660-1663.

- 12. M. Jung, J. Fuhrmann, A. Ferizi, G. Fischer, R. Weigel and T. Ussmueller, "A 10 GHz low-power multi-modulus frequency divider using Extended True Single-Phase Clock (E-TSPC) Logic," 2012 7th European Microwave Integrated Circuit Conference, Amsterdam, 2012, pp. 508-511.

- F. Stas and D. Bol, "A 0.4-V 0.66-fJ/Cycle Retentive True-Single-Phase-Clock 18T Flip-Flop in 28-nm Fully-Depleted SOI CMOS," in *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 65, no. 3, pp. 935-945, March 2018.

- 14. J. Lin, M. Sheu, Y. Hwang, C. Wong and M. Tsai, "Low-Power 19-Transistor True Single-Phase Clocking Flip-Flop Design Based on Logic Structure Reduction Schemes," in *IEEE Transactions on Very Large Scale Integration (VLSI)* Systems, vol. 25, no. 11, pp. 3033-3044, Nov. 2017.