# An Efficient Multiplier based on Rounding Technique for Accurate and High-Level Processing

Nasir husain<sup>1</sup>, Dr. Bharti Chourasia<sup>2</sup>

<sup>1</sup>MTech scholar, <sup>2</sup>Professor & Head <sup>1&2</sup>Department of Electronics and Communication, <sup>1&2</sup>RKDF Institute of Science & Technology, Bhopal, India.

*Abstract*: Multiplier is one in every of the foremost wide used arithmetic knowledge path operation in modern digital design. In the state of art Digital Signal process and graphics applications, multiplication is an important and computationally intensive operation. This paper proposed design and implementation of 64-Bit ROBA multiplier with low power, area and high speed. Existing 16 bit and 32 bit multipliers are using for signed numbers. Proposed multiplier support both signed and unsigned number as well as provide better performance than existing multipliers.

## IndexTerms - ROBA, VLSI, Multiplier, Speed, power.

## I. INTRODUCTION

Rounding technique is one of the most efficient methods for packing the input data before processing. This method has a potential to improve the circuit characteristics such as power and energy consumption, speed and area which is suitable method for the approximate computing. Approximate computing works very well to most of error resilient applications in the field of computer vision, image processing, pattern recognition, signal processing, scientific computing, and machine learning. Over past decade, research on these areas has given lots of opportunities in research. A multiplier is a fundamental block of computation and one of the most resource-consuming operations Rounding input data requires major responsibility in maintaining the accuracy. With a basic intuition, it can be stated that, rounding lower bits results in less error compared to rounding higher bits. Thus, the proposed algorithm has assigned rounding weights with respect to the bit position value.

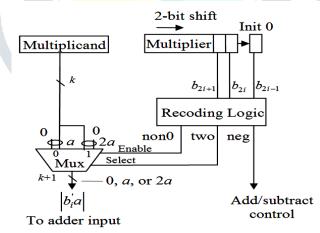

the execution of the multiplier can be incredibly improved. Be that as it may, the expenses are an unpredictable 'multiplexer' with zero, multiplicand, and twice multiplicand contributions, just as the carry-in information and one's supplement calculation required for negative numbers. Higher radix Stall's recoding can be utilized to additionally diminish the quantity of cycles however requires a significantly progressively complex multiplexer. Note that most iterative multipliers based on MBR neglect to successfully misuse the operand structure; accordingly, they are fixed cycle multipliers.

Figure 1: An iterative multiplier structure based radix-4 MBR

Notwithstanding the three foremost execution upgrade strategies listed above, there are extra procedures accessible for improving the execution of an iterative multiplier by diminishing the inertness per cycle and by planning effective structures for performing quick expansion, including, e.g., carry-look-ahead and carry select hardware.

## **II. LITERATURE SURVEY**

**P. Lohray et al.,[2019]** Approximate figuring is one of most appropriate effective information preparing for mistake versatile applications, for example, signal and picture handling, PC vision, AI, information mining and so forth. Approximate figuring decreases exactness which is worthy as an expense of expanding the circuit qualities relies upon the application. Alluring exactness is the limit point for controlling the exchange off, among precision and circuit attributes under the influence of the circuit originator. In this work, the rounding system is presented as an effective method for controlling this exchange off. In such manner multiplier circuits as a basic structure hinder for registering in a large portion of the processors have been considered for the assessment of the rounding procedure proficiency. The effect of the rounding method is researched by correlation of circuit qualities for three multipliers. These three multipliers are the ordinary Wallace tree precise multiplier, DRUM [4] the as of late

#### © 2020 JETIR February 2020, Volume 7, Issue 2

#### www.jetir.org (ISSN-2349-5162)

proposed approximate multiplier and the adjusted based approximate multiplier proposed in this work. Recreation results for three chose advances show critical enhancement for the circuit qualities as far as power, region, speed, and vitality for proposed multiplier in correlation with their partners. Info information rounding design and the likelihood of the redundancy for adjusted qualities has been acquainted as two fundamental things with control the degree of the precision for each scope of the information with least cost on the equipment. [1]

**M. S. Ansari et al.,[2019]** Logarithmic multipliers take the base-2 logarithm of the operands and perform augmentation by just utilizing movement and expansion tasks. Since registering the logarithm is often an approximate procedure, some precision misfortune is unavoidable in such plans. Be that as it may, the territory, inertness, and power consumption can be fundamentally improved at the expense of precision misfortune. This paper introduces a novel method to approximate log 2 N that, unlike the current methodologies, adjusts N to its closest power of two rather than the highest power of two littler than or equivalent to N. This guess strategy is then used to structure two improved 16×16 logarithmic multipliers that utilization correct and approximate adders (ILM-EA and ILM-AA, separately). These multipliers accomplish up to 24.42% and 9.82% investment funds in region and power-defer item, individually, contrasted with the best in class structure in the writing with comparative exactness. The proposed structures are assessed in the Joint Photographic Experts Group (JPEG) picture pressure calculation and their focal points over other approximate logarithmic multipliers are shown.[2]

**P. Lohray, et al.,[2019]** Approximate registering is one of most appropriate proficient information handling for blunder versatile applications, for example, signal and picture preparing, PC vision, AI, information mining and so on. Approximate figuring lessens exactness which is satisfactory as an expense of expanding the circuit attributes relies upon the application. Alluring precision is the edge point for controlling the exchange off, among exactness and circuit attributes under the influence of the circuit creator. In this work, the rounding strategy is presented as a proficient method for controlling this exchange off. In such manner multiplier circuits as a basic structure obstruct for registering in the greater part of the processors have been considered for the assessment of the rounding procedure proficiency. The effect of the rounding method is explored by examination of circuit attributes for three multipliers. These three multipliers are the regular Wallace tree exact multiplier, DRUM [4] the as of late proposed approximate multiplier and the adjusted based approximate multiplier proposed in this work. Recreation results for three chose innovations show critical enhancement for the circuit attributes regarding power, territory, speed, and vitality for proposed multiplier in examination with their partners. Information rounding design and the likelihood of the reiteration for adjusted qualities has been acquainted as two basic things with control the degree of the exactness for each scope of the information with least cost on the hardware.[3]

S. Vahdat, et al. [2019] A scalable approximate multiplier, called truncation-and rounding-based scalable approximate multiplier (TOSAM) is exhibited, which decreases the quantity of halfway items by shortening every one of the information operands dependent on their driving one-piece position. In the proposed plan, augmentation is performed by move, include, and little fixedwidth increase activities bringing about enormous upgrades in the vitality consumption and territory occupation contrasted with those of the definite multiplier. To improve the total exactness, input operands of the duplication part are adjusted to the closest odd number. Since input operands are shortened dependent on their driving one-piece positions, the precision turns out to be pitifully subject to the width of the info operands and the multiplier gets scalable. Higher upgrades in plan parameters (e.g., territory and vitality consumption) can be accomplished as the info operand widths increment. To assess the proficiency of the proposed approximate multiplier, its structure parameters are contrasted and those of a precise multiplier and some other as of late proposed approximate multipliers. Results uncover that the proposed approximate multiplier with a mean outright relative mistake in the scope of 11%-0.3% improves postponement, zone, and vitality consumption up to 41%, 90%, and 98%, separately, contrasted with those of the definite multiplier. It additionally outflanks other approximate multipliers as far as speed, region, and vitality consumption. The proposed approximate multiplier has a practically Gaussian blunder conveyance with a close to zero mean worth. We abuse it in the structure of a JPEG encoder, honing, and grouping applications. The outcomes show that the quality corruption of the yield is insignificant. What's more, we propose a precision configurable TOSAM where the vitality consumption of the duplication activity can be balanced dependent on the base required exactness. [4]

**L. Babu et al.,[2018]** Duplication is the urgent structure squares in picture handling, DSP applications. To make high-speed here utilizing an approximate multiplier this is a proficient one. For that the method is to rounding the estimations of numbers to the closest power of two. Utilizing this method the convoluted piece of duplication can be evacuated consequently can improve the speed of increase. This multiplier is relevant for both positive and negative number. The proficiency of this multiplier is investigations by contrasting and the precise multipliers lastly contemplated its productivity in picture preparing applications like picture smoothening and honing. The multiplier activity is at long last executed in FPGA Straightforward pack. [5]

**III. SIMULATION AND RESULT**

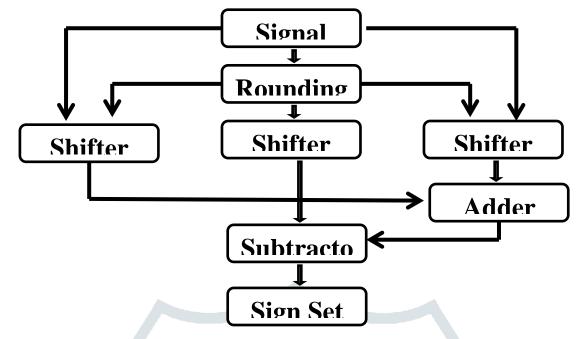

Figure 2: Flow Chart

It is proposed to design and analyze the performance of the ROBA multiplier for high speed digital signal processing. Check different parameters like speed, Look up table, time etc. To design ROBA multiplier. Simulate and synthesis using Xilinx 14.7. To test with different input combination and check speed and accuracy.

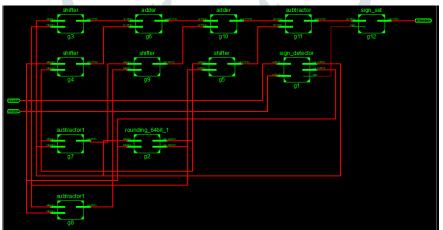

Figure 3: RTL of ROBA Multiplier

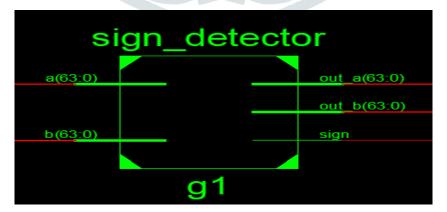

Figure 4: ROBA sign detector

In figure 4, showing one component of proposed multiplier i.e shifter, which can shift input data and send for next process.

## © 2020 JETIR February 2020, Volume 7, Issue 2

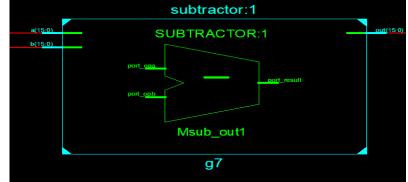

Figure 5: ROBA Subtractor

| Name            | Value                                   | <br>999,994 ps | 999,995 ps | 999,996 ps                              | 999,997 ps | 1999,998 ps | 999,999 ps | 1,000,000 ps |

|-----------------|-----------------------------------------|----------------|------------|-----------------------------------------|------------|-------------|------------|--------------|

| a[7:0]          | 2222222                                 |                |            | 2222222                                 |            |             |            |              |

| <b>b</b> [7:0]  | 22222222                                |                |            | 2222222                                 |            |             |            |              |

| aut[15:0]       | 200000000000000000000000000000000000000 |                |            | 000000000000000000000000000000000000000 | 0X         |             |            |              |

| 🌃 data_a[7:0]   | 200000000                               |                |            | X000000X                                |            |             |            |              |

| 🌃 data_b[7:0]   | XXXXXXXXXX                              |                |            | X000000X                                |            |             |            |              |

| ar[7:0]         | XXXXXXXXX                               |                |            | X0000000X                               |            |             |            |              |

| 📲 br[7:0]       | XXXXXXXXXX                              |                |            | X000000X                                |            |             |            |              |

| 16 sign         | x                                       |                |            |                                         |            |             | 1          |              |

| 🌃 brxa[15:0]    | 200000000000000000000000000000000000000 |                |            | 000000000000000000000000000000000000000 | ox 🛛       |             |            |              |

| anxb[15:0]      | xxxxxxxxxxxxxxxxxxx                     |                |            | 000000000000000000000000000000000000000 | ox 🛛       |             |            |              |

| 📲 arxbr[15:0]   | *****                                   |                |            | 000000000000000000000000000000000000000 | x          |             |            |              |

| adder_out[15:0] | xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx |                |            | 000000000000000000000000000000000000000 | x          |             |            |              |

| 🃲 sub_out[15:0] | 000000000000000000000000000000000000000 |                |            | 000000000000000000000000000000000000000 | ox.        |             |            |              |

| 6 n[31:0]       | 0000000000000000                        |                | 00000      | 000000000000000000000000000000000000000 | 000001000  |             |            |              |

|                 |                                         |                |            |                                         |            |             |            |              |

|                 |                                         |                |            |                                         |            |             |            |              |

|                 |                                         |                |            |                                         |            |             |            |              |

Figure 6: High impendence test bench bar

In figure 6, showing test bench bar for all possible value, which is also known as high impendence.

|                 | ar ror an p         |              |              |              |                                         |                 |              | 5r           |              |              |         |

|-----------------|---------------------|--------------|--------------|--------------|-----------------------------------------|-----------------|--------------|--------------|--------------|--------------|---------|

|                 |                     |              |              |              |                                         |                 |              |              |              | 2,000,000 ps |         |

| Name            | Value               | 1,999,992 ps | 1,999,993 ps | 1,999,994 ps | 1,999,995 ps                            | 1,999,996 ps    | 1,999,997 ps | 1,999,998 ps | 1,999,999 ps | 2,000,000 ps | 2,000,0 |

| 🕨 👹 out[127:0]  | 0000000000000000000 |              |              |              | 000000000000000000000000000000000000000 | 00000007d708834 |              |              |              |              |         |

| ▶ 🚮 a[63:0]     | 000000000000aaff    |              |              |              | 0000000                                 | 0000aaff        |              |              |              |              |         |

| <b>b</b> [63:0] | 000000000000bbcc    |              |              |              | 00000000                                | 000bbcc         |              |              |              |              |         |

|                 |                     |              |              |              |                                         |                 |              |              |              |              |         |

|                 |                     |              |              |              |                                         |                 |              |              |              |              |         |

|                 |                     |              |              |              |                                         |                 |              |              |              |              |         |

|                 |                     |              |              |              |                                         |                 |              |              |              |              |         |

|                 |                     |              |              |              |                                         |                 |              |              |              |              |         |

|                 |                     |              |              |              |                                         |                 |              |              |              |              |         |

|                 |                     |              |              |              |                                         |                 |              |              |              |              |         |

|                 |                     |              |              |              |                                         |                 |              |              |              |              |         |

|                 |                     |              |              |              |                                         |                 |              |              |              |              |         |

|                 |                     |              |              |              |                                         |                 |              |              |              |              |         |

|                 |                     |              |              |              |                                         |                 |              |              |              |              |         |

Figure 7: 64 Bit ROBA multiplier test bench in binary number

In figure 7, showing input a is aaff and input b is bbcc and output is 7D708834

Table 1: Comparison with Previous and proposed work

| Sr No.                         | Parameters         | Previous work | Proposed work |  |  |

|--------------------------------|--------------------|---------------|---------------|--|--|

| 1                              | Type of Multiplier | ROBA -32 bit  | ROBA – 64 bit |  |  |

| 2                              | Area               | 13.31%        | 12.25%        |  |  |

| 3                              | Delay              | 21.79ns       | 42.800ns      |  |  |

| 4                              | Accuracy rate      | 90 %          | 95%           |  |  |

| 6                              | Power              | 1.03mW        | 0.42mW        |  |  |

| 7 PDP (Power delay<br>product) |                    | 22.44         | 17.97         |  |  |

Therefore design and synthesis of ROBA multiplier using Xilinx verilog and find proposed multiplier is better than previous multiplier.

## **IV. CONCLUSION**

Therefore in this paper, design and analysis of rounding based approximate multiplier for digital signal processing. Consequently obviously such different is skilled to give quick increase of digital signal with high exactness. It additionally requires less investment and expends less territory. Presently, ROBA multiplier can be utilized in various digital signal applications.

In future work,

## © 2020 JETIR February 2020, Volume 7, Issue 2

- Modified ROBA multiplier which can give more accurate multiplication.

- Real time multiplication using different digital signal application.

- Make hardware implementation using FPGA kit.

## REFERENCE

P. Lohray, S. Gali, S. Rangisetti and T. Nikoubin, "Rounding Technique Analysis for Power-Area & Energy Efficient Approximate Multiplier Design," 2019 IEEE 9th Annual Computing and Communication Workshop and Conference (CCWC), Las Vegas, NV, USA, 2019, pp. 0420-0425.

www.jetir.org (ISSN-2349-5162)

- 2. M. S. Ansari, B. F. Cockburn and J. Han, "A Hardware-Efficient Logarithmic Multiplier with Improved Accuracy," 2019 Design, Automation & Test in Europe Conference & Exhibition (DATE), Florence, Italy, 2019, pp. 928-931.

- P. Lohray, S. Gali, S. Rangisetti and T. Nikoubin, "Rounding Technique Analysis for Power-Area & Energy Efficient Approximate Multiplier Design," 2019 IEEE 9th Annual Computing and Communication Workshop and Conference (CCWC), Las Vegas, NV, USA, 2019, pp. 0420-0425.

- 4. S. Vahdat, M. Kamal, A. Afzali-Kusha and M. Pedram, "TOSAM: An Energy-Efficient Truncation- and Rounding-Based Scalable Approximate Multiplier," in *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 27, no. 5, pp. 1161-1173, May 2019.

- 5. L. Babu and L. NM, "FPGA Implementation of Energy Efficient Approximate Multiplier with Image Processing Applications," 2018 2nd International Conference on Trends in Electronics and Informatics (ICOEI), Tirunelveli, 2018, pp. 637-641.

- 6. V. Leon, G. Zervakis, S. Xydis, D. Soudris and K. Pekmestzi, "Walking through the Energy-Error Pareto Frontier of Approximate Multipliers," in *IEEE Micro*, vol. 38, no. 4, pp. 40-49, Jul./Aug. 2018.

- 7. V. Leon, G. Zervakis, D. Soudris and K. Pekmestzi, "Approximate Hybrid High Radix Encoding for Energy-Efficient Inexact Multipliers," in *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 26, no. 3, pp. 421-430, March 2018.

- 8. T. Su, C. Yu, A. Yasin and M. Ciesielski, "Formal Verification of Truncated Multipliers Using Algebraic Approach and Re-Synthesis," 2017 IEEE Computer Society Annual Symposium on VLSI (ISVLSI), Bochum, 2017, pp. 415-420.

- R. Zendegani, M. Kamal, M. Bahadori, A. Afzali-Kusha and M. Pedram, "RoBA Multiplier: A Rounding-Based Approximate Multiplier for High-Speed yet Energy-Efficient Digital Signal Processing," in *IEEE Transactions on Very Large Scale Integration* (VLSI) Systems, vol. 25, no. 2, pp. 393-401, Feb. 2017.

- 10. J. Wang and S. Lin, "Efficient Sampling-Based ADMM for Distributed Data," 2016 IEEE International Conference on Data Science and Advanced Analytics (DSAA), Montreal, QC, 2016, pp. 321-330.

- 11. X. Liu and S. C. Draper, "The ADMM Penalized Decoder for LDPC Codes," in *IEEE Transactions on Information Theory*, vol. 62, no. 6, pp. 2966-2984, June 2016.

- 12. Y. Pauchard, R. J. Cintra, A. Madanayake and F. M. Bayer, "Fast computation of residual complexity image similarity metric using low-complexity transforms," in *IET Image Processing*, vol. 9, no. 8, pp. 699-708, 8 2015.

- 13. M. Abbas, O. Gustafsson and H. Johansson, "On the Fixed-Point Implementation of Fractional-Delay Filters Based on the Farrow Structure," in *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 60, no. 4, pp. 926-937, April 2013.

- J. Wang, S. W. H. de Haan, J. A. Ferreira and P. Luerkens, "Analytical analysis of the equivalent parasitic capacitance of the high-voltage cascade multiplier in medical application of X-ray power generator," *Proceedings of The 7th International Power Electronics and Motion Control Conference*, Harbin, 2012, pp. 463-470.