# Survey on Digital IF Filter with Low Complexity using Multi-rate System

Simra Haider, Dr. Vibha Tiwari

M. Tech. Scholar, Professor, Department of Electronics and Communication Engineering, TIT, Bhopal, India.

**Abstract**— Advanced Intermediate Frequency (IF) is the key innovation in programming radio territory. The DIF preparing module of shortwave base on programming radio innovation has DIF handling to include signal, at that point total Digital sign handling in advanced region. In the DIF handling module, A/D and D/A are significant. It asks the A/D converter have enough working transmission capacity (in excess of 2 GHz) and higher inspecting speed (60 MHz), and higher change digit to improve dynamic range. More and more people around the world suffer from digital signal processing research field. The increase hardware complexity and increase area are the main reasons for this field. The multi-rate approach used for narrow band filter will designed and implemented in Xilinx software.

Keywords: - Filter Coefficient, Intermediate Frequency, Pass-band Frequency, Narrow Band Filter.

## I. INTRODUCTION

In the field of aviation TTC framework, a ground station is for the most part used to catch and track airborne vehicles with the guide of an enormous high addition limited bar. Such a looking and following procedure works when the edge blunder locator of a recieving wire servo framework can distinguish the point mistake (counting azimuth blunder and pitch blunder) between laser whirligig inertial hub and reception apparatus pivot. After intensification and certain tasks, this edge mistake sign can drive a servo engine to make the electric reception apparatus hub go for the laser spinner inertial hub in order to acknowledge programmed following to the airplane [1, 2]. This customary technique is for the most part dependent on simple gadgets and advancements, which lead to some significant drawbacks, for instance, costly laser whirligig and huge size turntable reception apparatus.

With the progression of advanced gadgets and computerized signal handling innovation, another idea of advanced exhibit radar (DAR), which can splendidly join computerized innovation and reception apparatus innovation, rises to embrace DBF to supplant the customary simple pillar framing in both transmitting and accepting mode [3–5]. The key strategies of DAR for the most part incorporate advanced transmitter and recipient (T/R) module, multichannel computerized getting, fast and huge limit information transmission, wide band DBF, and superior programming signal handling. Multichannel computerized collector is the center of DAR due to its high equipment/programming multifaceted nature, high combination, and elite list.

Considering the exacting necessities for DAR with respect to address distinguishing proof of sufficiency and stage between different beneficiaries, DBF beneficiary embraces the idea of programming characterized radio (SDR) [6–8]. The focal thought of SDR is to build an open, institutionalized, and particular stage, which will utilize programming to achieve balance and demodulation capacities.

The fundamental structures of SDR can be generally isolated into three kinds: radio recurrence (RF) low pass inspecting, RF band pass testing, and IF band pass examining.

So as to improve the selectivity, stifle out-band obstructions, and lessen the preparing pace of the ensuing sign processor, radars generally embrace the IF band pass examining, which is an IF advanced recipient as a rule receiving very heterodyne framework [9]. Since the inspecting happens straightforwardly in middle of the road recurrence, the ensuing preparing would all be able to be taken care of in the advanced structure. This will defeat the deficiencies of the conventional recipients that depend on simple gadgets and simple sign handling system, for example, gain variety, DC temperature float, and nonorthogonality between and . Subsequently, the security and consistency can be altogether improved.

With the advancement and use of wideband high goals radar, the transfer speed of computerized beneficiaries gets progressively more extensive, and the inspecting rate is progressively higher. The structure of wideband IF computerized beneficiaries are more entangled than that of the restricted band IF advanced recipients [9], which are fundamentally reflected in the accompanying perspectives:

With the expansion of inspecting information rate, the subsequent sign preparing speed can't be stayed aware of. Likewise, the high information rate additionally prompts the issues of rapid information transmission and information synchronization.

Combinational recurrence obstruction inside a beneficiary is incredibly expanded. Hence, an advanced plan thinking about an assortment of is exceptionally basic.

RF front-end simple circuits of a recipient definitely have sufficiency and stage harshness, particularly for the wideband collectors. What's more, there is irregularity of the channel recurrence reaction, which would influence the side projection level, the yield sign to clamor proportion (SNR), or zero profundity of versatile pillar framing. Along these lines, the channel equalizer [10] must be received for revision.

It very well may be seen that the different channel computerized beneficiaries dependent on DBF are considerably more mind boggling than the conventional ones. In actuality, a DBF recipient may incorporate numerous channels, even up to a large number of channels. Be that as it may, there exist some stringent necessities for the collector measure and weight of airborne radar, space borne radar, or different radars.

To determine the previously mentioned issues, in this paper we propose a DAR beneficiary dependent on Multi-FPGA framework [11], which can give an enormous number of computerized to address the issue of advanced beneficiaries for computerized interface. The fast parallel preparing capacity dependent on Multi-FPGA equipment, develop IP centers, and advanced handling innovation can enormously encourage the structure of our computerized recipient, making it possible for constant application with the highlights of low power utilization, high thickness, and physical size scaling down.

# II. MULTIRATE APPROACH

The procedure of changing over a flag from an offered rate to an alternate rate is called testing rate transformation. The frameworks which utilize various examining rates in the handling of advanced flag are called multi-rate flag preparing [5].

Annihilation is the procedures of bringing down the word rate of a carefully encoded flag, which is inspected at high frequencies much over the nyquist rate.

It is typically done to build the goals of an oversampled flag and to expel the out-of-band clamor. In a sigma-delta ADC, oversampling the simple information motion by the modulator alone does not bring down the quantization commotion; the ADC should utilize an averaging channel, which fills in as a decimator to expel the clamor and to accomplish higher goals.

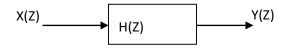

An essential square diagrammatic portrayal of the decimator is appeared in Figure 1. The decimator is a blend of a low pass channel and a down sampler. In Figure 1 the exchange work, H(z) is illustrative of performing both the activities. The yield word rate of the decimator is down inspected by the factor M, where M is the oversampling proportion [6]. The capacity of low pass separating and down testing can be done utilizing an averaging circuit. The exchange capacity of the averaging circuit is given by condition (1.1). It sets up a connection between the information and yield capacities (1.1)

After Decimator Sampling Frequency fs/M

Fig. 1: Block Diagram of Decimator

$$H(Z) = \frac{X(Z)}{Y(Z)} = \frac{1}{M} \sum_{x=0}^{M-1} Z^{-x}$$

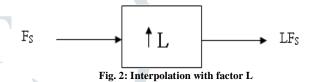

"Up sampling" is the way toward embeddings zeroesteemed examples between unique examples to expand the examining rate. (This is classified "zero-stuffing".) Up testing adds to the first flag undesired ghastly pictures which are fixated on products [7] of the first inspecting rate.

"Introduction", in the DSP sense, is the procedure of upexamining pursued by sifting. (The separating evacuates the undesired phantom pictures.) As a straight procedure, the DSP feeling of insertion is to some degree not the same as the "math" feeling of addition, yet the outcome is reasonably comparable: to make "in the middle of" tests from the first examples.

The outcome is as though you had quite recently initially tested your flag at the higher rate. Expanding the inspecting recurrence use interpolator is present.

Since addition depends on zero-stuffing you can just interject by number components; you can't insert by fragmentary variables. (Be that as it may, you can join insertion and annihilation to accomplish a general sane.

Factor, for instance , 4/5 up examining up desired phantom pictures to the flag at products of the first inspecting rate, so except if you expel those by separating, the up-tested flag [7] isn't equivalent to the first: it's contorted.

A few applications might have the capacity to endure that; for instance, if the pictures get expelled later by a simple channel, yet in many applications you should evacuate the undesired pictures through advanced sifting. Along these lines, introduction is undeniably increasingly normal [8] that up-inspecting alone.

## **III. LITERATURE REVIEW**

Hyobeen Park et al. (2018, [1]), because of constrained recurrence assets, new benefits are being applied to the current frequencies, and specialist co-ops are apportioning a portion of the current frequencies for recently upgraded versatile interchanges. Due to this recurrence condition, repeater and base station frameworks for versatile interchanges are getting progressively confused, and recurrence obstruction brought about by different groups and administrations is deteriorating. Hence, a heterodyne collector utilizing IF channels with high selectivity has been utilized to limit the obstruction between frequencies. Notwithstanding, repeater and base station frameworks in versatile correspondences utilizing fixed IF channels can't effectively adapt to the utilization of different recurrence groups, the use of different administrations, and recurrence reusing. Subsequently, this brief proposes a reconfigurable advanced IF channel with variable focus recurrence and data transfer capacity while accomplishing high selectivity as existing IF channels. The middle recurrence of channel can change from 10MHz to 62.5MHz, and the channel data transmission can be specific to one of 10MHz, 15MHz, and 20MHz. The proposed computerized channel likewise decreases the multifaceted nature of adders and multipliers by 38.81% and 41.57%, individually, contrasted with a

(1)

current advanced channel by utilizing a channel bank and a multi organize structure.

Dwaipayan Ray et al. [2], single steady duplication (SCM) and different consistent increases (MCM) are among the most prevalent plans utilized for low-intricacy move include usage of limited drive reaction (FIR) channels. While SCM is utilized in the immediate structure acknowledgment of FIR channels, MCM is utilized in the transposed direct structure structures. Regularly, the cross breed structure FIR channels where the sub-areas are executed by fixed-size MCM squares give better territory, time, and power productivity than those of customary MCM and SCM based usage. To have an effective half breed structure channel, in this paper, we have played out an itemized intricacy investigation regarding the equipment and time devoured by the crossover structure structures. We find that the current half and half structure structures lead to an unwanted increment of unpredictability in the basic snake square. Thusly, to have a progressively productive usage, a variable size dividing approach is proposed in this paper. It is indicated that the proposed methodology expends less zone and gives about 11% decrease of basic way delay, 40% decrease of intensity utilization, 15% decrease of zone postpone item, 52% decrease of vitality defer item, and 42% decrease of intensity territory item, on a normal, over the best in class techniques.

Mohammed Alawad al. (2017, [3]), high et unpredictability presents memory/stockpiling serious difficulties to accomplishing high throughput and high vitality effectiveness in discrete 2-D FIR sifting. This exhibition bottleneck is particularly intense for implanted picture or video applications that utilization 2-D FIR preparing broadly, on the grounds that ongoing handling force and low power utilization are their foremost structure goals. Luckily, the vast majority of such discernment based installed applications have purported "intrinsic adaptation to internal failure", which means slight registering exactness debasement has pretty much nothing if not no negative impact on their nature of results, yet has critical ramifications to their throughput, equipment execution cost and vitality productivity. This paper builds up a novel stochastic-based 2-D FIR sifting design that adventures the notable probabilistic convolution hypothesis to accomplish both low equipment cost and high vitality effectiveness while accomplishing exceptionally high throughput and figuring vigor. Our ASIC combination results show that, for a 2-D FIR channel size  $(4 \times 4)$ , input square size (L = 4), and picture size (512  $\times$  512), our stochastic-based engineering accomplishes L yields per cycle with 29.79 occasions and multiple times less zone delay-item (ADP), and 4.39 occasions and 3.02 occasions less power utilization contrasted and the regular structure and as of late distributed cutting edge, separately.

**A. Mehrnia et al. [4],** half band channels utilized in multigiga test per-second radio recurrence/middle of the road recurrence information converters to interject or demolish the sign are answerable for an impressive segment of the power utilization. We presently realize that the affectability of half band channels to coefficient quantization can be efficiently decreased. This can be misused in the channel configuration procedure to yield half band channels with decreased equipment multifaceted nature, prompting lower control utilization as well as higher working velocities. The general induction of such desensitized half band structures and the connection between their coefficients and those of regular half band channels are introduced. Rhythm usage results show noteworthy enhancements.

S. Dhabu et al. [5], reconfigurable channels dependent on the ghostly parameter estimate (SPA) procedure and its mix with different systems give a consistent power over the cutoff recurrence (f c ). In any case, when wide f c range and limited change transmission capacity is wanted, these channels either neglect to fulfill a portion of the particulars or have amazingly high multifaceted nature. In this short, we propose an introduced SPA (ISPA) channel that defeats every one of the confinements of all the current SPA procedure based channels, and accomplishes exceptionally wide f c run (equivalent to around the whole Nyquist band) and restricted change data transfer capacity alongside little passband wave and high stopband constriction. Examination with the cutting edge reconfigurable channels is given by means of a plan model, which shows that the ISPA channel accomplishes over half reserve funds in the quantity of multipliers contrasted with the channel dependent on the blend of SPA and adjusted coefficient pulverization systems. The field-programmable door exhibit usage results show that the ISPA channel has a lot lesser gathering deferral and a lot higher working rate, however acquires moderate punishment as far as territory contrasted with the channel dependent on the blend of recurrence change and introduction systems.

## IV. PROPOSED STRUCTURE

In this work the design of a decimation filter is presented for integrating with an existing designed modulator to form a complete sigma-delta ADC. We use multi-organize destruction channel which implies the single pulverization channel is supplanted by fell channels. In this part, we will discuss the channel engineering utilized in this work, including their structures, qualities and downsides. the initial phase in structuring an obliteration channel is to choose which sorts of channels will be utilized and where demolition will happen. This section investigates the issues associated with picking channel design for a listening device application. The general intensity of a few designs is analyzed, bringing about the three-arrange engineering that is picked to actualize this channel.

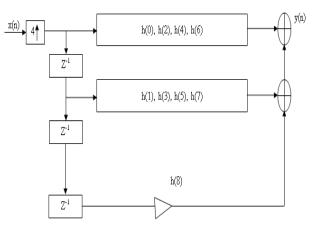

Fig. 3: Interpolator structure with filter order N3=9 and L=4

## © 2020 JETIR September 2020, Volume 7, Issue 9

| Sampling frequency,                    | $F_s = 250Hz$                                    |

|----------------------------------------|--------------------------------------------------|

| Pass band ripple,                      | $\delta_p = 0.08 dB$                             |

| Stop band ripple, $\delta_s = 42$      | 2dB                                              |

| Pass band frequency,                   | $f_{p} = .825 Hz$                                |

| Stop band frequency,                   | $f_{s} = 4.15 Hz$                                |

| $rac{x(n)}{F_s}$ $4 \downarrow$ $h(0)$ | ), h(4), h(3), h(12) $U(n)$<br>F <sub>8</sub> /4 |

| h(1                                    | ), h(5), h(9), h(13)                             |

Fig. 4: Decimator structure with filter order N1=17 and M=4

A typical need in gadgets and DSP is to confine a restricted band of frequencies from a more extensive data transmission flag. Narrowband channels rather catch just a little piece of the range. They are said to have a thin band-pass. The bandpass is basically the amount of the range the channel permits to pass. This is typically estimated in nanometers. Limited band channel comprises of decimator, restricted band and interpolator.

#### V. CONCLUSION

The narrowband filter is realized in FIR filter. Based on the direct approach, the filter requires 150 filter coefficients to meet the desired frequency response. To implement such a large order FIR filter in hardware involves large resources and sometime difficult to implement in resource constrained application. Keeping this in view, we have used Multirate approach to design the narrowband filter. We have used down sampling factor 2 and 4 for this purpose and found that, down sampling factor 4 requires significantly less filter constants than 2. To implement the narrowband filter, we therefore chosen down sampling factor 4 and designed the decimator, interpolator and narrowband filter. The total number of filter coefficients required to realize the decimator, interpolator and the narrowband filter 64 which is almost 58% less than the direct method.

## REFERENCE

- Hyobeen Park, Myoungseok Yu, Yunho Jung, and Seongjoo Lee, "Design of Reconfigurable Digital IF Filter with Low Complexity", IEEE Transactions on Circuits and Systems II, 2018.

- [2] Dwaipayan Ray, Nithin V. George, and Pramod Kumar Meher, "Efficient Shift-Add Implementation of FIR Filters Using Variable Partition Hybrid Form Structures", IEEE Transactions On Circuits And Systems–I: Regular Papers, Vol. 32, Issue 6, June 2018.

- [3] Mohammed Alawad and Mingjie Lin, "Memory-Efficient Probabilistic 2-D Finite Impulse Response (FIR) Filter", IEEE Communication Letters, Vol. 99, No. 04, April 2017.

- www.jetir.org (ISSN-2349-5162)

- [4] A. Mehrnia, M. Dai, A. N. Willson, "Efficient half band FIR filter structures for RF and IF data converters", IEEE Transactions on Circuits and Systems II: Express Briefs63, no. 1 (2016): 64-68.

- [5] S. Dhabu, and A. P. Vinod, "Design and FPGA Implementation of Reconfigurable Linear-Phase Digital Filter With Wide Cutoff Frequency Range and Narrow Transition Bandwidth", IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 63, no. 2, pp. 181-185, 2016

- [6] Basant Kumar Mohanty, and Pramod Kumar Meher, High-Performance FIR Filter Architecture for Fixed and Reconfigurable Applications", IEEE Transactions on Very Large Scale Integration (VLSI) Systems, Vol. 78, No.06, April 2016.

- [7] Indranil Hatai, Indrajit Chakrabarti, and Swapna Banerjee, "An Efficient VLSI Architecture of a Reconfigurable Pulse-Shaping FIR Interpolation Filter for Multi-standard DUC", IEEE Transactions on Very Large Scale Integration (VLSI) Systems, Vol. 23, No. 6, June 2015.

- [8] Sang Yoon Park and Pramod Kumar Meher, "Efficient FPGA and ASIC Realizations of DA-Based Reconfigurable FIR Digital Filter", IEEE Transactions on Circuits And Systems-Ii: Express Briefs, 2014.

- [9] Pramod Kumar Meher, Sch. of Autom., IEEE, Shrutisagar Chandrasekaran, Member, IEEE, andAbbes Amira, Senior Member, IEEE, "Distributed Arithmetic for FIR Filter implementation on FPGA", Proceedings of IC-BNMT 2011.

- [10] Ms. S.Manjui, Mr. V. Sornagopae, "An Efficient SQRT Architecture of Carry Select Adder Design by Common Boolean Logic", 978-1-4673-5301-4/13/\$31.00 ©2013 IEEE.

- [11] Basant K. Mohanty, And Pramod Kumar Meher, "A High-Performance Energy- efficient Architecture For FIR Adaptive Filter Based On New Distributed Arithmetic Formulation Of Block LMS Algorithm", in IEEE Transactions on Signal Processing, Vol. 61, No. 4, PP. No. 45-52, February, 2013.