ISSN: 2349-5162 | ESTD Year : 2014 | Monthly Issue JOURNAL OF EMERGING TECHNOLOGIES AND INNOVATIVE RESEARCH (JETIR) An International Scholarly Open Access, Peer-reviewed, Refereed Journal

# Heat Energy Based Power Routing of Solid State Transformer with CSI and DAB Converters

T. A. Sunil Raj<sup>1</sup> M.Kalyanasundari<sup>2</sup> S.Jerome Singh<sup>3</sup>

<sup>1,2,3</sup>Assistant Professor <sup>1,2,3</sup>Department of Electrical & Electronics Engineering <sup>1,2,3</sup>PSN Institute of Science and Technology, Tirunelveli, India

Abstract—The Solid state transformer (ST) is a potential solution for an upgrade of the electric distribution grid, which enables to provide services to the grid and dc-connectivity. However, the power electronics within the system are challenged by high reliability requirements. One possible solution to increase the reliability is to employ prognosis to predict the failures and avoid down times of the system. Traditional maintenance scheduling is based on the Remaining Useful Lifetime (RUL) of the individual components or the forecasted failure probability. For a further increase of the time to the next maintenance, it is desired to have similar wear out of all components, which need to be maintained or exchanged. In this work, it is proposed to route the power internally in a modular power converter consisting of a Current Source Inverter connected to dual active bridges in order to influence the remaining useful lifetime of its building blocks. Therefore, a heat stress based wear-out control is designed for addressing the processed power dependent failures of the devices in the building blocks of the ST. Compared to the conventional power routing methods, the impact of the proposed system-level control considering electrical and heat parameter variations is demonstrated using Monte Carlo analysis.

## I. INTRODUCTION

The paradigm shift from fossil fuels to green-technologies in the energy production has altered the conventional power system network with higher share of renewable energy sources and electric vehicle charging stations. This has posed challenges in the electrical distribution network with spatially distributed generations and bidirectional power flow. The ST is a promising solution to address the power flow flexibility while catering the requirements of changing grid scenarios [1], [2]. However, expected lower reliability is one of the key challenges of the ST compared with the conventional low frequency transformer.

One of the possible solutions to increase the system reliability is to carry out maintenance schedules based on prognosis. Prognosis is a technical process resulting in the determination of RUL. There are many scientific publications regarding the prognostic maintenance scheduling in high reliability industrial applications, aviation sector etc. [3], [4]. However, fewer references investigate the maintenance scheduling focusing on the system level control algorithms to delay the maintenance. Since the ST is a modular system with multiple stages possibly located in remote areas, frequent maintenance schedules can result in very high costs. Therefore, a system level heat stress controller is proposed to optimize the maintenance schedules. In order to develop a system level heat stress control, the critical components and factors are to

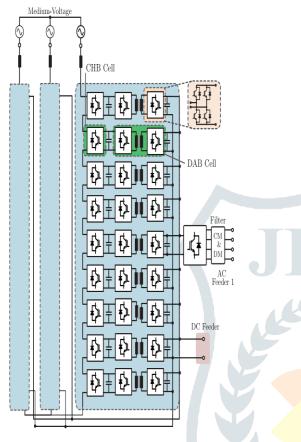

be identified. Power electronic devices and capacitors contribute to the major failures in converter systems [5], [6]. Power cycling of the devices resulting in heat cycles is considered to be the crucial factor for the aging of devices. The existing literature mainly focuses on device level and converter level reliability by actively controlling the heat cycles by different methods such as switching frequency control, active gate drivers and modulation techniques [7]–[9]. For improving the reliability of a modular converter system comprising of many cells, the aging of the cells can be actively controlled by unequal sharing of the power depending on the remaining useful life of each module [10], [11]. Power routing using virtual resistance method is studied for low voltage inverter of the ST in [12]. For an ST composed of CSI and DAB converters, power routing technique with virtual resistance is introduced in [13]. This work studies the impact of unequal power sharing on the reliability of the ST on a system level and the development of a power routing controller for the overall system. Power routing is achieved using virtual resistances for heat stress control in the modular ST comprised of Current Source Inverter (CSI) converter cells and Dual Active Bridge (DAB) cells as shown in Fig. 1. Virtual resistances provide the power references for each unit of the ST depending on the aging of that unit. The control of power flow through the cells based on their aging results in heat stress based wear-out control of the overall system. Thus the maintenance scheduling can be optimized in order to reduce the maintenance costs. Compared to the virtual resistance based methods in [12] and [13], a generalized validation of the impact of a system level power routing technique considering parameter variations using Monte Carlo analysis is provided in this work. Moreover, detailed analysis and experimental results along with a collector emitter voltage sensor for junction temperature estimation are presented as well.

The paper is organized as follows. Section II introduces the investigated ST architecture and provides the motivation for the heat stress based wear-out control. Design of the heat stress based power routing controller based on virtual resistances is explained in section III. Section IV discusses the implementation of the proposed power routing scheme in the laboratory setup and the effect on heat stress due to power routing is illustrated.

## www.jetir.org (ISSN-2349-5162)

Heatudy dies der achigh fabiguse Tanad déades, toosly strechtwievel lifte aft. stnets is work or threlle on dis wipe op biosofd is to consistentized at het hemain internative remechanism less ince the heat fatigure of the solder joints become prominent only with very high heat swings (greater than 100K) [16], [17]. The power processed by the semiconductor module determines the amount of loss dissipation in the module and consequently the junction temperature. Power processed by the ST varies according to the grid conditions and results in the variation of device junction

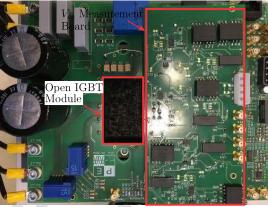

Fig. 2: Open IGBT module with Vcemeasurement.

| TABLE I: ST specification. |       |              |                |      |

|----------------------------|-------|--------------|----------------|------|

| Rated Power                | MVAC  | LVAC         | Grid frequency | LVDC |

| 1MVA                       | 10 kV | 400 <i>V</i> | 50Hz           | 800V |

Da

temperature. For fatigue analysis, Miner's rule can be applied to calculate the accumulated damage using [18]

$$N_i$$

$$cc = \sum N_{fi}$$

(2)

where  $D_{acc}$  is the accumulated damage,  $N_i$  the number of cycles and  $N_{fi}$  the durability of the *i*-th stress range. When the accumulated damage becomes 1, the device fails.

## B. Investigated ST Architecture

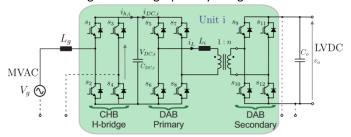

The investigated ST architecture is composed of a modular structure CSI and DAB converters. AC-DC stage is realized by the CSI converter and the DC-DC stage by the DAB converter. CSI converter connected to the MVAC grid rectifies the AC voltage into DC. DAB DC-DC converters convert the rectified DC-link voltage of each CSI cell into low voltage DC while providing the isolation between MV and LV side. Fig. 1 shows the system architecture. The system parameters are listed in Table I.

To implement a heat stress control, junction temperature measurement of the devices is necessary. The collector emitter voltage ( $V_{ce}$ ) is one of the most reliable temperature dependent electrical parameter to monitor the health of the device [19]. Hence the modular cells of the ST are equipped with  $V_{ce}$ sensing system as shown in the Fig. 2. Moreover, the junction temperature estimation from the  $V_{ce}$ sensing makes the implementation of the heat stress based control algorithms more practical.

Fig. 1: ST architecture with CSI and DAB.

## II. POWER ROUTING IN ST ON SYSTEM LEVEL

This section introduces the reliability challenges in the ST and lays down the theoretical background of the proposed strategy for improving the reliability of the ST. The system description of the ST prototype is also presented.

## A. Semiconductor Reliability Challenges

As discussed in the introduction, power electronic devices are one of the main sources of failures and thereby posing challenges to the reliable opeartion of the ST. To analyze the root cause of failures in power semiconductors, Physics of-Failure (PoF) approach has become the state of the art. Accordingly, the junction temperature fluctuations influence the aging and deterioration of the power modules as expressed in (1). Here,  $N_f$ denotes the number of heat cycles to failure depending on the heat swing  $\Delta T$ , average junction temperature  $T_{j,av}$  and the device dependent parameters  $a_1$ ,  $a_2$  and  $a_3$ . The parameter  $a_2 \approx 5$  makes  $N_f$  highly sensitive to junction temperature variations [14], [15].

$$N_f = a_1(\Delta T)_{a_2} \cdot e_{T_{i},a_{v+273} \circ C}$$

JETIR2307441 Journal of Emerging Technologies and Innovative Research (JETIR) <u>www.jetir.org</u> e403

(1)

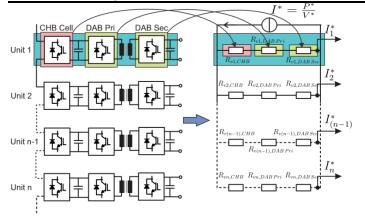

Fig. 4: Equivalent circuit design of virtual resistor based power routing in the ST with CSI and DAB.

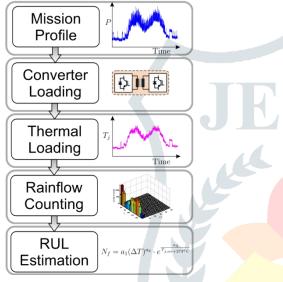

Fig. 5: Calculation of device wear-out from heat cycling based on operating conditions.

## III. DESIGN OF VIRTUAL RESISTANCE BASED POWER ROUTING CONTROLLER

If the ST is composed of cells of different ages, equal heat stress due to equal power sharing results in failures of cells at different instants, leading to frequent maintenances. Therefore, a power routing strategy based on virtual resistances is developed in this section to equalize the heat stress among the differently aged cells.

1) Concept of Virtual Resistance: In the proposed strategy, each converter cell in the modular ST is represented by a resistor indicating the aging of that particular cell. This is shown graphically in Fig. 4 where the CSI and DAB cells in the ST architecture are represented by resistors. The more aged cell has a higher resistance than a new cell. Thus the total current is divided among the units according to the combined resistance of each units as depicted in Fig. 4. Since the resistors are implemented in software to generate the current/power references, they are termed as virtual resistors.

#### www.jetir.org (ISSN-2349-5162)

*2) Design of Virtual Resistance for Power Routing:* The virtual resistance design is shown graphically in Fig. 5.

Fig. 6: Detailed schematic of CSI and DAB converter unit in the ST. Since the converters are equipped with  $V_{ce}$  junction temperature sensing system as shown in Fig. 2, the junction temperature profiles are obtained directly. This junction temperature profile of the past time period can be used to calculate the consumed lifetime  $\Delta D_i$  of each cell using rainflow counting and the lifetime model as described in section II [18]. Subsequently, the total accumulated damage can be calculated for each converter using (3)

$$D_i = \sum \Delta D_i \tag{3}$$

where  $(D_i)$  is the accumulated damage of the *i*<sup>th</sup>cell. Based on the accumulated damages of the semiconductor modules, the power distribution is changed to delay the power dependent failures.

As depicted in Fig. 4, Rvi,CSI,IGBT, Rvi,CSI,DIODE, Rvi,DABPri and  $R_{vi,DABSec}$  are calculated from their respective accumulated damages using the relation (4)

Virtual reistor

$$\propto D_i$$

(4)

$R_{vi,CSLIGBT}$  and  $R_{vi,CSLDIODE}$  are the virtual resistance values for the IGBTs and diode in the CSI respectively, whereas  $R_{vi,DABPri}$  and  $R_{vi,DABSec}$  represent the virtual resistance values of primary and secondary side of DABs. For the next step, a weighted average of the virtual resistances of CSI and DAB modules in one power path is considered for the total virtual resistance calculation as expressed in (5).

## $R_{vi}=w_{i}$ , CSI, IGBT · $R_{vi}$ , CSI, IGBT + $w_{i}$ , CSI, DIODE · $R_{vi}$ , CSI, DIODE + $w_{i}$ , DAB · $max(R_{vi}$ , DABPri,

$R_{vi,DABSec}$ ,  $i\varepsilon$ [1,N](5)

The maximum virtual resistance value among the twobridges  $(max(R_{vi,DABPri},R_{vi,DABSec}))$ , is chosen for calculation (5) because both bridges process the same power and the bridge with higher virtual resistance is expected to fail first. For the CSI, however, power routing has relatively little impact on the total losses [11]. The damage accumulation of the most damaged IGBT and diode in a cell are considered for modeling CSI virtual resistance.

Finally, the power reference  $P_i^*$  is obtained by solving the virtual resistor network as illustrated in Fig. 4. For a system with N = 3 cells, the power references  $P_1^*, P_2^* P_3^*$  are given by TABLE II: System parameters

| Symbol                        | Description                 | Value                      |

|-------------------------------|-----------------------------|----------------------------|

| <i>e</i> (rms)                | Grid voltage (rms)          | 230 <i>V,</i> 50 <i>Hz</i> |

| Lg                            | Filter inductance (MV side) | 3.8mH                      |

| <i>VDC</i> ,1 = <i>VDC</i> ,2 | DC-link voltage reference   | 250V                       |

| Vo                            | DC-link voltage (LV side)   | 250V                       |

| n                             | MFT turn ratio              | 1:1                        |

|     | fsw,CSI      | Switching frequency of the CSI | 3kHz  |

|-----|--------------|--------------------------------|-------|

|     | $f_{sw,DAB}$ | Switching frequency of the DAB | 12kHz |

| (6) |              |                                |       |

Therefore, the higher the value of virtual resistance, lower the processed power through each unit. The total power of the system is divided among the cells according to the value of the virtual resistance for the cell.

It is to be noted that for the implementation of power routing, the converters are not over-sized and when the system is operated under full load, the converters process their rated power. The power routing strategy is active only during the partial load operation and the distribution transformer such as the ST operates at partial load for most of the time.

#### IV. IMPLEMENTATION OF POWER ROUTING

In order to realize the testing of the proposed power routing controller with virtual resistors, a control scheme for scaled down prototype of ST with five level CSI and two DABs has been developed in this section.

#### A. Control Scheme for CSI and DAB

Fig. 6 shows the detailed schematic of a unit composed of one CSI cell and one DAB cell. The unit is taken as the building block for MVAC to LVDC conversion because if one of the cells in a unit fails, the power cannot flow through that unit since the cells are connected in series. For the studies, the device parameters described in section III are utilized and the system parameters are given in Table. II.

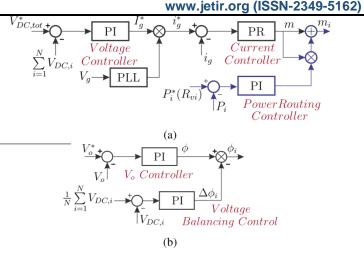

The overall control strategy for CSI and DAB converters in the ST is shown in Fig. 7 (a) and (b) respectively. The CSI rectifier stage controls and shapes the input ac current and controls the total MVDC-link voltage. The current and voltage control is achieved through cascaded controller structure with Proportional-Resonant (PR) controller and ProportionalIntegral (PI) controller respectively [20]. The power references ( $P_i^*$ ) generated by the virtual resistors are given to the power routing controller as depicted in Fig. 7 (a). The modulation index, *m*, produced by the PR controller is modified by the PI-based power routing controller to achieve different power flow through the DC-links of CSI.

A control scheme with output and input voltage control is adopted for the DAB as shown in Fig. 7 (b). The input MVDC link voltages are balanced by the DAB, which is critical for the stability while processing unequal power through each Hbridge of the CSI. For the output LVDC-link voltage control,

Fig. 7: (a) CSI control scheme with power routing controller (b) DAB control scheme.

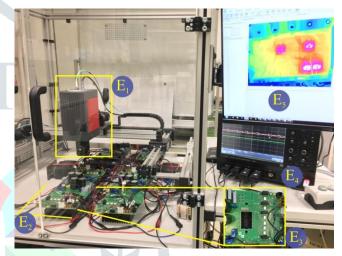

Fig. 8: The experimental setup ( $E_1$  - High Speed Heat Camera,  $E_2$ -CSI and DABs,  $E_3$  - Open Module,  $E_4$  -Oscilloscope,  $E_5$  - Heat image.

a PI voltage controller is designed using pole-zero cancellation technique [21].

#### B. Experimental Validation of Power Routing Controller

To validate the proposed power routing control strategy, a small scale prototype of a five level CSI connected to two DABs has been developed as illustrated in Fig. 8. The H-bridges of CSI and DAB are made with open-module

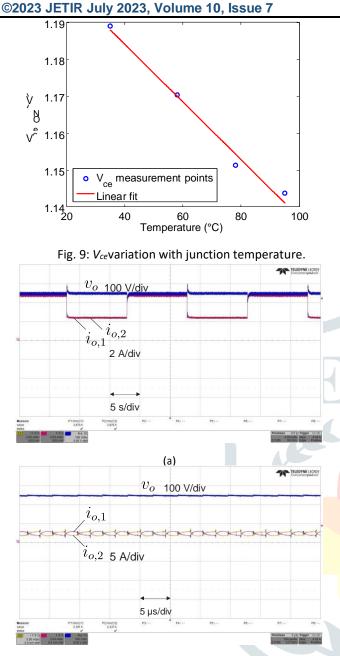

DP25H1200T101616 from Danfoss to facilitate direct junction temperature measurements. A high speed infrared heat camera is used to obtain the heat response of the power semiconductors of the open module. The camera is controlled by an automatic positioning system for fast and accurate measurements. The setup is controlled by dSPACE SCALEXIO system. The  $V_{ce}$  measurement board integrated to each converter cell provides the junction temperature information and this is validated using the heat camera. The variation of the  $V_{ce}$ vs. temperature is shown in Fig. 9 and subsequently,

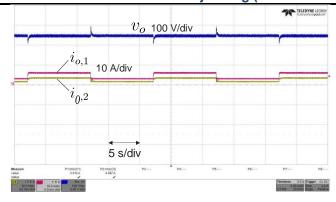

Fig. 10: (a) The output currents of both DABs  $(i_{0,1-2})$  and the load voltage  $(v_0)$  for equal power sharing for the given mission profile (b) The output currents of both DABs  $(i_{0,1-2})$  and the load voltage  $(v_o)$  with time scale  $5\mu s/div$ .

(b)

the junction temperature is estimated using a fitting model for the selected device.

The controller of the ST should be able to maintain the reference LVDC voltage even when the power flowing through each unit is different. Moreover, the CSI DC-link voltages should be balanced and must be equal to their reference value. The proper functioning of power routing controller is tested by changing the power distribution among the ST units.

When the power routing is not activated, the DABs share the power equally as shown in the Fig. 10. Here, a mission profile with a step change from  $P_n$ = 1.2kW to  $P_n$ = 2.4kW with each power cycle lasting for 10s is applied as the input for the ST.

## www.jetir.org (ISSN-2349-5162)

Fig. 11: The output currents of both DABs  $(i_{0,1-2})$  and the load voltage  $(v_o)$  with activated power routing controller for the given mission profile.

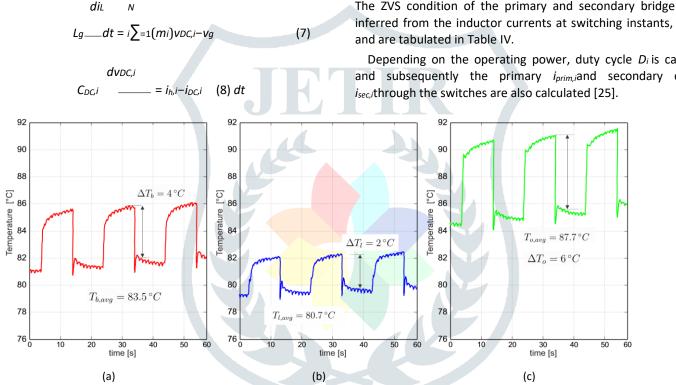

This results in the different remaining useful lifetimes of the cells and the Table III depicts the number of cycles to failure for the three cases using (1). The lifetime in Table III is normalized with respect to that of balanced power sharing. By lowering the heat cycling in lightly loaded cell, the RUL has increased by 38 times. In this case, the lifetime of the overloaded cell has reduced by 10 times compared to that of balanced operation. The reduction of lifetime of overloaded

cell is less that of the increase in lifetime for the lightly loaded cell. The IGBT is rated for 25A rms and is operated with a much lower current, and hence the lifetime reduction of overloaded cell is lower. This shows that the at lower power levels, a net increase of the system lifetime is achieved through TABLE III: Normalized number of cycles to failure  $(N_f)$  for equal and unequal power sharing

| Case                | <i>N<sub>f</sub></i> (norm.) |

|---------------------|------------------------------|

| Balanced            | 1                            |

| Over-loaded cell    | $\frac{1}{10}$               |

| Lightly-loaded cell | 38                           |

power routing.

The objective of the experiment is to validate the working of the designed power routing controller and it's effect on the junction temperature and consequently the aging. It is clear that the power routing controller can influence the junction temperature of the modules and thereby the stress on the semiconductors in different cells of the ST.

#### V. IMPACT OF PROPOSED METHOD ON THE RELIABILITY OF THE ST

Scientific references perform the lifetime analysis based on analytical models [22], [23]. Therefore, in this work, an electroheat simulation model along with lifetime models are considered to analyze the reliability of the ST. In order to incorporate the deviations of the simulation parameters in a practical scenario, a sensitivity analysis using Monte Carlo simulation is performed and the results are analyzed in this section.

## A. Methodology of Reliability/Lifetime Study

The methodology of lifetime estimation is presented in Fig. 5. In order to analyze the lifetime using the heat stress analysis, a mission profile is used to generate the working condition of the power converter. Depending on the mission profile, the heat

loading of the converter is obtained using an electro-heat model of the system. Once the junction temperature fluctuations are known, the lifetime can be calculated using the rainflow counting method and a lifetime model of the power device.

#### B. Design of Electro-Heat Model of ST for Validation of VR based PR

In order to conduct a lifetime analysis of the ST, an electro heat model of 10 CSI cells connected to 10 DAB cells are modeled in MATLAB. The model consists of electrical equations of CSI and DAB along with heat models of the semiconductor switches and the heatsink for calculating the junction temperature of each device.

1) CSI modeling : The unit comprising of CSI connected to DAB cell as shown in Fig. 6 is considered for describing the system model. The current and voltage in CSI is modeled using the electrical equations (7) and (8) from Fig. 6 [24],

Fig. 12: Variation of primary side IGBT junction temperatures over time of the DAB cells for (a) Balanced operation (b) where  $m_i$  is the modulation index of each H-bridge. Lightly loaded cell (c) Over loaded cell.

| Case                    | Primary Bridge | Secondary Bridge |

|-------------------------|----------------|------------------|

| $I_1 > 0$ and $I_2 > 0$ | ZVS            | ZVS              |

| $I_1 > 0$ and $I_2 < 0$ | non-ZVS        | ZVS              |

| $I_1 < 0$ and $I_2 > 0$ | ZVS            | non-ZVS          |

When the powers processed by each H-bridge are equal, the modulation index applied to each of them are also equal. In case of power unbalance, the modulation index of the Hbridges varies [24]. Since the H-bridges are connected in series in the CSI, the total current flowing through each H-bridge remains the same. However, depending on the modulation index, the current sharing among the diodes and IGBTs changes.

2) DAB modeling: Considering phase shift modulation for DAB cell *i*, the power is given by

where  $P_i$  is the power processed by DAB cell *i*,  $m_{DAB,i}$  is the modulation index of the cell DAB<sub>i</sub>, V<sub>DCi</sub>is the MVDC link voltage, L<sub>i</sub>is the leakage inductance and  $T_{SW,DAB}$  is the switching time period.

In order to determine the ZVS operation, the inductor currents at the switching instants  $D = \frac{i}{2} T^{sw}$  and  $T = \frac{sw,DAB}{2}$  are given by

$$I_1 = [(2D-1)+M]$$

(10)

4 $L_i$

$$V_{DC,i}T_{sw,DAB}$$

$$I_2 = [1+M(2D-1)] \qquad (11)$$

The ZVS condition of the primary and secondary bridge can be inferred from the inductor currents at switching instants, I1 and I2

Depending on the operating power, duty cycle D<sub>i</sub> is calculated and subsequently the primary *i*prim,iand secondary currents

3) Device modeling and loss calculation: Once the current through the devices are obtained from the CSI and DAB models, the power losses are computed. The device used is the IGBT module DP25H1200T101616 from Danfoss and the device parameters are obtained experimently in [26]. The switching losses (P<sub>(sw,igbt)</sub>) and the conduction losses (P<sub>cond,igbt</sub>) of the IGBT are given by the equations.

$$P_{\text{sw,igbt}} = - \begin{bmatrix} \sum_{n=1}^{N_{\text{sw}(\text{on})}} E_{\text{on}} (V_{\text{ce}}, I_c, T_j) \\ T + \sum_{n=1}^{\text{sw}(\text{off})} E_{\text{off}} (V_{\text{ce}}, I_c, T_j) \\ 1 Z T \\ P_{\text{cond,igbt}} = - V_{ce}(I_c(t), T_j) \cdot I_c(t) dt \\ T = 0 \end{bmatrix}$$

(13)

**JETIR2307441** Journal of Emerging Technologies and Innovative Research (JETIR) www.jetir.org e407

where  $N_{sw(on)}$  and  $N_{sw(off)}$  are the number of turn-on and turn-off instants of the IGBT for the time interval *T*,  $V_{ce}$  is the collectoremitter voltage,  $I_{ci}$  is the current flowing through the IGBT and  $T_{j}$  is the IGBT junction temperature.

For computing diode losses such as the reverse recovery losses ( $P_{rec}$ ) and conduction losses ( $P_{cond,diode}$ ), equations (14) and (15) are used.

$$P_{\text{rec}} = \frac{1}{T} \sum_{n=1}^{N_{\text{sw}}} (f, I_f, T_d) = E_{\text{rec}} V$$

$$T$$

$$P_{\text{cond,diode}} = \frac{\frac{1}{T}}{T} \int_{0} (V_{flf}(t), T_d) \cdot I_f(t) dt$$

(15)

Here,  $E_{rec}$  is the reverse recovery energy of the diode,  $V_f$  is the forward voltage drop,  $I_f$  is the current flowing through the diode,  $V_f$  is the voltage across the diode and  $T_d$  is the diode die temperature.

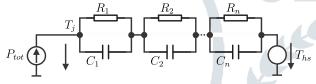

4) Heat network modeling: In order to calculate the junction temperature from the losses, a heat network of the power device with the heatsink is modeled and the junction temperatures thus obtained is fed back for the loss computation. The heat model consists of a Foster network with ther-

Fig. 13: Heat model for IGBT and diode in the power module connected to the heatsink.

## C. Validation of the Impact of Power Routing on the ST on System Level

To evaluate the impact of power routing on wear-out based failures in the ST, a RUL estimation study without and with the power routing control has been carried out. The methodology shown in Fig. 5 is used for lifetime analysis. The ST with 10 units comprised of ten CSI cells are fed with mission profile to evaluate the wear-out based failure. It is assumed that all the cells have zero wear-out due to heat cycling at the beginning of operation. The electrical parameters affecting the losses of the converters and the heatsink temperatures are different for the each cell according to normal distribution. When the accumulated damage reaches unity according to (2), the cells are assumed to reach their end of life.

Without any heat stress control, the individual CSI and DAB cells have different heat cycling due to the differences in electrical and heat parameters. Therefore, the wear-out of each cells are different and this leads to their failure at different times. The electro-heat model of the ST

#### www.jetir.org (ISSN-2349-5162)

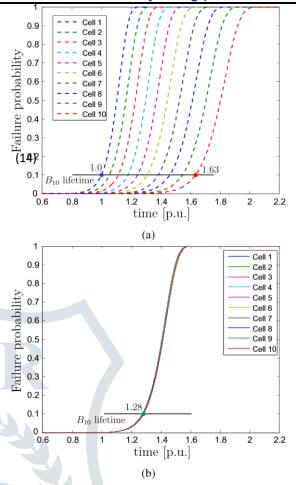

Fig. 14: Unreliability of the DAB cells (a) without power routing (b) with power routinggenerates the heat cycling profile of the cells in accordance with the mission profile, and subsequently the wearout based remaining useful lifetimes are calculated. Table V summarizes the results of the heat stress based lifetime evaluation. The RUL values are normalized for CSI and DABs by the failure of first CSI and DAB cell respectively. The first CSI cell fails in 19<sup>th</sup> year and the first DAB cell in 18<sup>th</sup> year and these values are considered as the base value for per unit (p.u.) calculations.

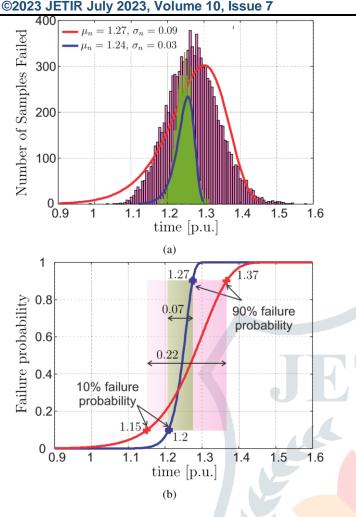

Fig. 16: Monte Carlo analysis without and with power routing control (a) Distribution of failures over time (b) Unreliability or cumulative probability distribution over time.

$F^{(t)} = 1 - \exp\left[-\left(\frac{t}{\alpha}\right)^{\beta}\right]$ (17)

The unreliability curves for the DAB cells without and with heat stress based power routing control is as shown in Fig. 14 (a) and (b) respectively. Here, the cells are replaced when they reach 10% failure probability, also commonly known as the  $B_{10}$  lifetime [22]. Without power routing it is clear from Fig. 14 (a) that the DAB cells are replaced at different instants.

In order to control the heat stress based aging, the power sharing between the units of the ST are dynamically changed according to the developed virtual resistor based power routing. The results of the case study are given in Table V. Compared to the conventional equal power sharing, the power routing method can effectively converge the RUL of the DAB cells, whereas it results in an improvement of the total estimated lifetime of the CSI cells. The power routing has lower impact in changing the loss distribution among the CSI cells due to the series connection of the cells. Whereas, for the DAB cells, the unequal power sharing can effectively vary the device losses and hence the heat cycling based wear-out is actively controlled. Failure of the first CSI cell is delayed by 19% with power routing strategy and that of the DAB cell is delayed by 28%.

When the heat stress control is applied, the failure probability of the cells converge and the  $B_{10}$  lifetime becomes 1.28 p.u as shown in Fig. 14 (b). Thus the number of maintenance can be reduced by manipulating the heat stress among the cells. However, the mean

#### www.jetir.org (ISSN-2349-5162)

RUL for DABs is decreased by 1.3% with the power routing method. On the other hand, for the CSI cells, a slight increase in the mean RUL of 0.5% is obtained by adopting the proposed control strategy.

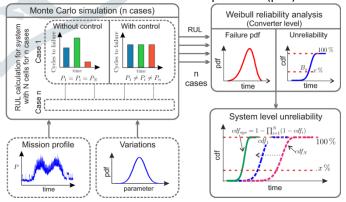

1) Analysis of Heat Parameter Sensitivity on Power Routing Control : For sensitivity analysis considering the heat parameter variations, a Monte Carlo simulation for 1000 cases with and without power routing is carried out using the system model. The schematic representation of the analysis is shown in Fig 15. Here, the heat parameters such as heatsink temperature and device parameters are considered as normal distribution with a standard deviation of 5% to emulate a real operating environment. The mission profile input along with the parameters given as the inputs to the electro-heat model generates the number of cycles to failure or RUL of the system for two cases; without heat stress control and with power routing for heat stress control. As illustrated in Fig 15, the Monte Carlo simulation is performed for n cases and the RUL thus obtained follows a Weibull distribution. Subsequently, the pdf and cdf of the Weibull distribution of individual converter cells are calculated. Finally, a system level unreliability/cdf is obtained using the formula given in (18),

$$cdf_{sys}=1-\prod_{i=1}(1-cdf_i)$$

where  $cd f_{sys}$  denotes the system level cdf and  $cd f_i$  indicates the cdf of a cell *i*.

Ν

Fig. 16 (a) shows the failure distribution of the ST with 10 DAB cells over the years with Monte-Carlo analysis. During the normal operation without active heat stress control, the earliest wear-out based failures start around 19 years (considered as 1 p.u.) and reaching the maximum probability of failure around 1.27p.u. years. The failure distribution approximated by a Weibull distribution has the mean and standard deviation as 1.27p.u. and 0.09p.u. respectively. From the Weibull distribution, the unreliability or the cumulative failure probability distribution can be obtained as shown in Fig 16 (b). Unreliability plot illustrates clearly the spread of failure distribution without any heat stress control. Here, 80% of failures are spread over 0.22p.u. time, making the maintenance scheduling difficult.

To evaluate the impact of power routing, Monte-Carlo analysis is repeated for the ST model with the virtual resistance based power routing control. The heat parameters of the system remain the same as that of the normal operation. The heat stress control is able to achieve a 3 times reduction in the standard deviation of failures compared to that of normal operation. However, the mean lifetime of the system is slightly decreased by 2.4% in comparison with normal operation. Fig. 16 (b) depicting the unreliability curve vividly demonstrates the advantage of the proposed strategy. In this case, 80% of failures occur in a span of 0.07 p.u., resulting in a better maintenance scheduling. Moreover, the  $B_{10}$  lifetime of the system is improved by 4.4% or 11.4 months as shown in Fig. 16 (b).

#### VI. CONCLUSION

For applications requiring very high reliability such as the ST, one of the possible solutions to increase the system reliability is to carry out maintenance schedules based on prognosis. Therefore, a power routing strategy for improving the reliability of power devices through heat stress based wear-out control is adopted.

Compared to the state of the art, a systematic development of a virtual resistance based system level control is presented, along with its validation in case of heat and electrical parameter variations using Monte Carlo analysis. Monte Carlo analysis shows that the proposed strategy is able to reduce the standard deviation of the failure probability by 3 times compared to that of normal operation. Moreover, the proposed strategy improves the  $B_{10}$  lifetime of the system resulting from heat stress based wear-out of the devices by 4.4% or 11.4 months. Experimental results demonstrate the potential of the Solid state transformer control system to route the power internally to achieve heat stress control.

#### REFERENCES

- A. K. Sahoo and N. Mohan, "Modulation and control of a single-stage hvdc/ac solid state transformer using modular multilevel converter," in 2017 IEEE Applied Power Electronics Conference and Exposition (APEC), March 2017, pp. 1857–1864.

- [2] X. She, A. Q. Huang, and R. Burgos, "Review of solid-state transformer technologies and their application in power distribution systems," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 1, no. 3, pp. 186–198, Sept 2013.

- [3] F. Camci, "System maintenance scheduling with prognostics information using genetic algorithm," *IEEE Transactions on Reliability*, vol. 58, no. 3, pp. 539– 552, Sept 2009.

- [4] C. S. Byington, M. J. Roemer, and T. Galie, "Prognostic enhancements to diagnostic systems for improved condition-based maintenance [military aircraft]," in *Proceedings, IEEE Aerospace Conference*, vol. 6, 2002, pp. 6– 2815–6–2824 vol.6.

- [5] F. Blaabjerg, K. Ma, and D. Zhou, "Power electronics and reliability in renewable energy systems," in 2012 IEEE International Symposium on Industrial Electronics, May 2012, pp. 19–30.

- [6] S. Yang, A. Bryant, P. Mawby, D. Xiang, L. Ran, and P. Tavner, "An industrybased survey of reliability in power electronic converters," *IEEE Transactions* on Industry Applications, vol. 47, no. 3, pp. 1441–1451, May 2011.

- [7] M. K. Bakhshizadeh, K. Ma, P. C. Loh, and F. Blaabjerg, "Indirect heat control for improved reliability of modular multilevel converter by utilizing circulating current," in 2015 IEEE Applied Power Electronics Conference and Exposition (APEC), March 2015, pp. 2167–2173.

- [8] H. Luo, F. Iannuzzo, K. Ma, F. Blaabjerg, W. Li, and X. He, "Active gate driving method for reliability improvement of igbts via junction temperature swing reduction," in 2016 IEEE 7th International Symposium on Power Electronics for Distributed Generation Systems (PEDG), June 2016, pp. 1–7.

- [9] Power Electronics, vol. 26, no. 4, pp. 1215–1227, April 2011.