# JETIR.ORG ISSN: 2349-5162 | ESTD Year : 2014 | Monthly Issue JOURNAL OF EMERGING TECHNOLOGIES AND INNOVATIVE RESEARCH (JETIR)

An International Scholarly Open Access, Peer-reviewed, Refereed Journal

# **KEY GENERATION OF AES ALGORITHM**

# B Sai Deepika, M.Tech student, Department of Electronics and Communication Engineering,

Cryptography is related to the system of converting ordinary undeniable text into unintelligible textual content and vice versa. Symmetric key algorithms namely Advanced Encryption Standard (AES), and Data Encryption Standard use the equal key for encryption and decryption. It is lots quicker, easy to put into effect and requires much less processing strength. Because of Side Channel attack where attackers Key leaked during the encryption process such as power consumption, or at execution time. The featuring Key extraction will be from the photo pixel so one can accept to the encryption and decryption of AES with out the use of the schematic key to enhance the security of the data when Key leakage from insiders threats or from improper key storage.

**Keywords** : AES (Advanced Encryption Standard), LUT (Look up table), Sub bytes, shift rows, mix column, add round key.

#### 1. Introduction

In ultra-modern virtual age, where sensitive statistics is constantly transmitted and stored electronically, information safety is of paramount significance. One of the cornerstones of contemporary cryptographic strategies is the advanced Encryption trendy (AES). AES is a symmetric-key encryption set of rules that has emerge as the de facto standard for securing information and communique channels. In this essay, we are able to discover the significance, history, and internal workings of AES.

The need for secure verbal exchange and information protection has been a steady concern since the sunrise of the digital generation. Cryptography, the technological know-how of cozy communication, has developed over time to fulfill the growing challenges posed via facts breaches and cyberattacks. Within the late 20th century, the facts Encryption fashionable (DES) turned into the reigning encryption trendy. But, as computational electricity accelerated, DES's fifty six-bit key period have become inadequate for strong protection. This caused the improvement of AES.

Published is the symmetric key block known as Advanced Encryption Standard (AES).aided by the national Institute of Standards and Technology (NIST) in December 2001. It is by far a non-Feistel block cypher that encrypts and JNTUCEA, Anantapur, Andhra Pradesh,India

Abstract :

decrypts a predetermined 128-bit information block. Three distinct key lengths exist. For 128-bit keys, 12 rounds of processing are involved in the encryption/decryption process, and 14 rounds are involved for 192-bit keys and 256-bit keys..

One method of converting regular, simple writing into incomprehensible text and vice versa is called cryptography. Hash characteristics, public key cryptography, and symmetric key cryptography are the three types of cryptographic techniques. Superior encryption is particularly popular with symmetric key techniques (AES),statistics Common encryption methods have an equal key for both encryption and decryption. It requires significantly less electricity for processing and is far quicker and simpler to implement.

The efficiency of AES is also a key component in its sizeable adoption. At the same time as providing a high degree of safety, it's miles designed to be computationally green and may be applied in both hardware and software program, making it appropriate for a wide variety of applications.

Inside the virtual landscape, AES performs a vital function in making sure the privacy and integrity of facts. It is utilized in diverse eventualities, from securing online transactions and communications to encrypting documents and protective touchy statistics. Moreover, AES is a essential aspect of cryptographic protocols like SSL/TLS, which might be important for securing web site visitors.

The study of secrecy, or hidden writing, is called cryptography.

It has two predominant components:

Encryption

concealing messages as a habit so theycan't be examine by means of everybody other than the supposed recipient

• Authentication & Integrity

Verifying the identity of individuals utilising information and sources and confirming that no message has been covertly changed

Necessities of comfortable verbal exchange

• Secrecy

The message is only known to the purported recipient.

• Authentication

Both the sender and the recipient must authenticate each other.

Message Accuracy

# 2. Literature survey

# 2. 1 Literature Review Paper-1

**Title :** "An Evaluation framework for security algorithms performance realization on FPGA" IEEE Transactions **Authors :** S.P. Guruprasad, B.S. Chandrasekar

**Outcome :** They were given For customers who desire less information protection, the DES Cipher, with its 1112.188 Mbps speed, is the best option. For better-facts safety, the users to put in force 888.804 Mbps of throughput is provided by AES-128. Additional calculations and logs have been made for other factors, including key duration, data length, and range of iteration cycles.

#### 2.2 Literature Review Paper-2

**Title :** "FPGA Based Hardware Implementation of AES Rijndael Algorithm for Encryption and Decryption" IEEE Transcations

Authors : N. S. Sai Srinivas ;MD. Akramuddin;

**Outcome** : Overall latency is significantly lower, with normal encryption and decryption times of 20–30 and 40 clock cycles, respectively,. It has a very high throughput. The completed throughput falls inside the zero range. For encryption, ninety-1.28 Gbps and zero. 6-0.85 Gbps in relation to decryption.

#### 3. Architecture

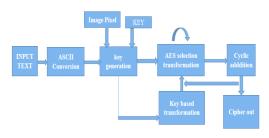

Fig 1: Block diagram of key Extraction

#### Using MATLAB

An photo includes tens of millions of pixels.

Each pixels includes 8-bits. Which can be converted into Hexadecimal statistics

Those converted information is stored in a single textual content report files. From the documents we can keep the information in Verilog memory format. Via making use of exclusive concatenation operation, we are able to make our key for AES encryption and decryption procedure.

The converted hexa-decimal data which stored in the file as mentioned above will called to the Model Sim the encryption and decryption processes as demonstrated in the below architecture.

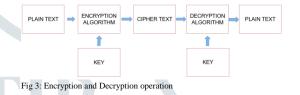

Fig 2 : Architecture of Extracted Key giving to AES

The architecture of AES is primarily based on properlydefined and mathematically sound principles. It operates using a symmetric-key technique, which entails using the same key for both encryption and decryption. AES helps key lengths of 128, 192, and 256 bits, presenting varying stages of security.

The set of rules may be summarized in a series of key steps:

#### Substitute Bytes:

The encryption website uses SubBytes as the primary transformation.. It uses a substitution table to do autonomous, non-linear byte replacement on every byte in the country (S-box). Every one of the state's sixteen bytes is replaced with the matching values that can be found on the research desk.. In decryption, InvSub Bytes is used. Bytes of a state are substituted from InvSubBytes table.

### Shift Rows:

Within the nation's bytes are moved to the left in each row during encryption. Shift Rows procedure is the name given to it. The number of shifts depends on the row-wide variety (0, 1, 2, or 3) of the national matrix. Rows one through three have their bytes moved to leave at least one, two, or three bytes remaining, but row zero's bytes remain unshifted.

#### Mix Column:

At the column level, the MixColumns transformation functions. It makes every column in the country into a new column. Without a doubt, the transformation is the result of multiplying a country column in a matrix by a steady square matrix. With the Galois field, all arithmetic operations are performed (Finite subject). Rather than being handled as numbers, the bytes are handled as polynomials.

#### Add Round Key:

A single column at a time is processed by AddRoundKey.. It's miles much like MixColumns in this recognize. AddRoundKey provides a round key-word to a matrix of columns. The AddRoundKey step is where matrix addition is accomplished.

We're producing Every five cycles, a 128-bit key, in order that it calls for most effective 1 S package in one cycle.

In traditional method, we want single S container for key technology block.

The cycle 14 mix operation may employ the 128-bit key that was created in the cycle.

General we need seventy four clock cycles to finish AES encryption.

### 4. Simulation tool

Software:XilinxISE14.7,ModelSim,Matlab 2018.A HDL: Verilog

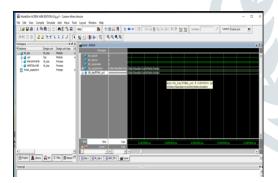

The software this is used to test and replicate the layout s capability. Modelsim- or ISE can be invoked for simulation. The key origination is secret. (among 10 keys generated). The manner selected pixels are mixed and its overlapping intensity is mystery.

In each cycle, we do operations in accordance with words (32 bits). Variety of blocks needed for both the suggested (32-bit) and conventional (128-bit) implementations are as follows:

The given input plain text

Plaintext=128'hcfdebcfdaedbbcfcadfefdebbcfad

Undeniable text will shuffle with the image pixel which converted into the hexa decimal key

Which was done by random selective method. After Encryption and Decryption the awaiting output text need to be same to the given plain text

Finaloutput 128'hcfdebcfdaedbbcfcadfefdebbcfadd

5. Results

#### Simulation End Result

Fig 4 :Simulation end result

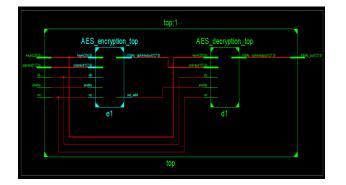

#### **RTL Schematic**

Fig 5: RTL Schematic

#### **Technology Schematic**

Fig 5: Technology Schematic

#### 6. Conclusion

This paper affords a generalized layout and a realistic implementation of AES algorithm with key extracted from photograph pixel. Rather than the usage of static key, the proposed technique had higher overall performance in phrases of safety while the key leakage or side channel attack happens.

#### 7. References

[1] M. Rajeswara Rao, Dr.R.K.Sharma, SVE Department, NIT Kurushetra "FPGA Implementation of combined S box and Inv S box of AES" 2017 4th International conference on signal processing and integrated networks (SPIN).

[2] Nalini C. Iyer ; Deepa ; P.V. Anandmohan ; D.V. Poornaiah "Mix/InvMixColumn decomposition and resource sharing in AES".

[3] Xinmiao Zhang, Student Member, IEEE, and Keshab K. Parhi, Fellow, "High Speed VLSI architectures for the AES Algorithm", IEEE. VOL.12. No.9. September 2004

[4] Shrivathsa Bhargav, larry Chen, abhinandan Majumdar,

Shiva Ramudit "128 bit AES Decryption", CSEE 4840 –

Embedded system Design spring 2008, Columbia University.

[5] Atul M. Borkar; R. V. Kshirsagar; M. V. Vyawahare "FPGA implementation of AES algorithm".

[6] Announcing the ADVANCED ENCRYPTION STANDARD (AES), November 26 2001.

[7] Yulin Zhang ; Xinggang Wang; "Pipelined implementation of AES encryption based on FPGA" 2010IEEE International Conference on Information Theory and Information Security.

[8] Yuwen Zhu ; Hongqi Zhang ; Yibao Bao ; "Study of the AES Realization Method on the Reconfigurable Hardware"2013 International Conference on Computer Sciences and Applications.

[9] Tsung-Fu Lin ; Chih-Pin Su ; Chih-Tsun Huang ; Cheng-Wen Wu; "A high-throughput low-cost AES cipher chip"Proceedings. IEEE AsiaPacific Conference on ASIC.

#### © 2023 JETIR November 2023, Volume 10, Issue 11

[10] C. Sivakumar ; A. Velmurugan ; "High Speed VLSIDesign CCMP AES Cipher for WLAN (IEEE 802.11i)" 2007International Conference on Signal Processing,Communications and Networking.

[11] Vatchara Saicheur ; Krerk Piromsopa ; "An implementation of AES128 and AES-512 on Apple mobile processor" 2017 14th International Conferenceon Electrical Engineering/Electronics, Computer, Telecommunications and Information Technology (ECTI-CON)

[12] S.P Guruprasad ; B.S Chandrasekar ; "An evaluation framework for security algorithms performance realization on FPGA" 2018 IEEE International Conference on Current Trends in Advanced Computing (ICCTAC)

[13] N. S. Sai Srinivas ; Md. Akramuddin; "FPGA based hardware implementation of AES Rijndael algorithm for Encryption and Decryption" 2016 International Conference on Electrical, Electronics, and Optimization Techniques (ICEEOT).

[14] P. S. Abhijith ; Mallika Srivastava ; Aparna Mishra ; Manish Goswami ; B. R. Singh ; "High performance hardware implementation of AES using minimal resources" 2013 International Conference on Intelligent Systems and Signal Processing (ISSP).

[15] Wei Wang ; Jie Chen ; Fei Xu ; "An implementation of AES algorithm Based on FPGA" 2012 9th International Conference on Fuzzy Systems and Knowledge Discovery