# Power Management Techniques and Its Impact in VLSI design

## Dr. G.C.Manjunath Associate prof.Dept of E&CE PDIT ,HOSPET

Abstract

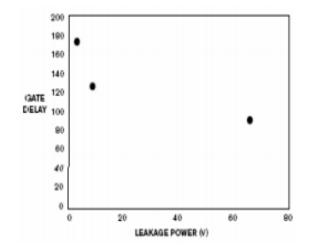

Appropriate innovation choice is one of the key parts of energy administration. The objective of every innovation headway is to enhance execution, thickness, and power utilization. The average approach in building up another age of innovation is to apply steady electric-field scaling. Process originators scale both the connected voltage and the oxide thickness to keep up a similar electric field. This approach diminishes control by around half with each new innovation hub However, as the threshold voltage the voltage gets littler. additionally should downsize to meet the execution focuses of that innovation. This scaling sadly expands the subthreshold current and thus the leakage control. To beat this imperative, process builds never again apply consistent field scaling for procedures of 65 nm or littler; rather, they utilized a more summed up type of scaling.

## 1.Introduction

Since it is difficult to streamline an innovation for both execution and leakage without a moment's delay, every innovation ordinarily has two variations. One variation goes for superior, and alternate shoots for low leakage. The essential contrasts between the two are in the oxide thickness, supply voltage, and threshold voltage. The innovation variation with the thicker door oxide goes for low-leakage plan and should bolster a higher voltage to accomplish a sensible execution. While choosing an innovation to enhance the power for a given plan, you should think about the two angles: the need to utilize a littler geometry to diminish dynamic power and the need to utilize a low-leakage variation to decrease leakage.

After selecting technology, the focus is on design techniques to optimize power. One has to start by selecting the appropriate logic gate from the standard cell library. Each gate in a standard cell library uses the smallest transistors and has multiple versions with different drive strengths, sizes, delays, multiple-threshold voltage and power consumption. Because the main parameter for controlling active power is the power-supply voltage, cell designers typically design and characterize the gates to operate at voltages as much as 30% lower than the power-supply voltage.

Lowering the power-supply voltage produces smaller currents, resulting in more delay. However, this slowdown is acceptable if the design is not pushing the edges of a given technology. Increasing the threshold voltage reduces the leakage current in the device. Leakage power also controlled by designing logic gates with multiplethreshold-voltage devices, including standard high and low threshold voltage devices.

## 2.LOW POWER MANAGEMENT IN PHYSICAL DESIGN

Physical outline apparatuses translate the power goal and actualize the format effectively, from position of uncommon cells to steering and advancement crosswise over power areas within the sight of various corners, modes, and power states, in addition to assembling inconstancy. An inexorably regular strategy to lessen control in physical plan is the utilization of different voltage islands (areas), which enables a few pieces to utilize bring down supply voltages than others, or to be totally stopped for specific methods of task.

Tickers are a huge wellspring of dynamic power utilization. Low-control clock tree blend (CTS) techniques incorporate bringing down general capacitance and limiting changing movement to accomplish control sparing. In any case, getting the best power comes about because of CTS relies upon the capacity to blend the tickers for various corners and modes simultaneously within the sight of plan and assembling inconstancy, and in multivoltage streams.

Power gating strategy is successful for decreasing leakage control by incidentally killed the circuit. This brief shutdown time can likewise call as "low power mode" or "idle mode". At the point when circuit squares are required for task indeed they are initiated to "dynamic mode". Closing down the squares can be proficient either by programming or equipment. Presently a-days a devoted power administration controller is utilized for this reason. Following table gives the trade-off associated with the various power management techniques.

The need for lower power systems is being driven by many market segments. Unfortunately designing for low power adds another dimension to the already complex design problem and the design has to be optimized for power as well as Performance and Area.

| Power Reeducation<br>Technique                       | Power<br>Benefit | Timing<br>Penalty | Area Penalty | Methodology Impact |        |              |                    |

|------------------------------------------------------|------------------|-------------------|--------------|--------------------|--------|--------------|--------------------|

|                                                      |                  |                   |              | Architecture       | Design | Verification | Implementatio<br>n |

| Multi VT<br>optimization                             | Medium           | Little            | Little       | Low                | Low    | None         | Low                |

| Clock Gating                                         | Medium           | Little            | Little       | Low                | Low    | None         | Low                |

| Multi supply<br>voltage                              | Large            | Some              | Little       | High               | Medium | Low          | Medium             |

| Power Shut off                                       | Huge             | Some              | Some         | High               | High   | High         | High               |

| Dynamic and<br>adaptive voltage<br>frequency scaling | Large            | Some              | Some         | High               | High   | High         | High               |

| Substrate Biasing                                    | Large            | Some              | Some         | Medium             | None   | None         | High               |

#### **Power Management Techniques and Its Impact**

The need for lower power systems is being driven by many market segments. Unfortunately designing for low power adds another dimension to the already complex

3.various issues and major challenges regarding low power designs are:-

• Technology Scaling: - It relates with the accompanying variables like: Capacitance per hub diminishes by 30%, Electrical hubs increments by 2X, Die estimate develops

design problem and the design has to be optimized for power as well as Performance and Area

> by 14% (Moore's Law), Supply Voltage lessens by 15% and Frequency Increases by 2X. To meet these issues moderately 2.7 X dynamic power will increment.

Leakage power: - To take care of recurrence demand Vt will be scaled which comes about high leakage control. A low voltage/low threshold innovation and circuit configuration approach, focusing on supply voltage around 1V and working with decreased thresholds.

- Dynamic power management techniques, varying supply voltage and execution speed according to the activity measurement.

- Low power interconnect, using advance technology, reduced swing or activity approach.

- Development of power conscious techniques and tools for behavioral synthesis, logic synthesis and layout optimization.

- Power saving techniques that recycle the signal energies using the adiabatic switching principals rather them dissipating them as a heat and promising in certain applications where speed can be trades for low power.

As there will turn into an expanding quantities of versatile. battery controlled systems, more consideration will be centered around low-control plan methods. The craft of low power configuration used to be a thin claim to fame in simple circuit plan. As the issue of vitality proficiency turns out to be significantly more unavoidable, the fight to utilize the absolute minimum of vitality will be battled on numerous semiconductor fronts: innovation, circuit configuration, outline robotization instruments, engineering, working system system, and application plan.

It is currently showing up in the standard advanced outline group influencing all parts of the plan procedure. In the long run, the worry for lowcontrol configuration will extend from gadgets to modules to whole systems, including application programming.

mechanical building At and level vitality utilization can be diminished by lessening the supply voltage, decreasing the capacitive load and by diminishing the exchanging recurrence. Much benefit can be picked up by keeping away from superfluous movement at both the building and system level. At system level, the system planner can exploit control administration highlights where accessible, and additionally disintegrated system designs and programming strategies for decreasing force utilization.

Some low-control plan procedures are additionally used to outline fast circuits, and to expand execution. For instance, streamlined code runs quicker, is littler, and along these lines additionally expends less vitality. Utilizing a reserve in a system enhances execution, as well as in spite of the fact that requiring more space utilizes less vitality since data is kept locally. The approach of utilizing application-particular coprocessors isn't just more proficient regarding vitality utilization, yet has additionally an execution increment on the grounds that the particular processors can do their undertaking more productive than a broadly useful processor.

## 4.Conclusion

The result is that despite the fact that the application-particular coprocessor approach is more effective than a broadly useful processor, it is less adaptable. Besides, the dormancy from the client's point of view is expanded, in light of the fact that a system in rest must be aroused up. Programmability is imperative for portable systems since they work in a powerfully changing condition and should have the capacity to adjust to the new condition. While low-control arrangements are as of now accessible for application particular issues, applying these arrangements in a reconfigurable situation is a generously more difficult issue, since programmable gadgets frequently bring about huge execution and vitality utilization punishments.

## **5.REFERENCES**

1.Agrakshi et al., Low Power Design Techniques in CMOS Circuits: A Review, International Journal for Research in Applied Science & Engineering Technology, 2015, Vol. 3, Issue 2, pp. 330-335.

2.Anu Tonk et al., A Literature Review on Leakage and Power Reduction Techniques in CMOS VLSI Design, International Journal on Recent and Innovation Trends in Computing and Communication, 2015, Vol. 3, Issue 2, pp. 554-558

3.KSSK Rajesh et al., CMOS VLSI Design of Low Power Comparator Logic Circuits, Asian Journal of Scientific Research, 2014, Vol. 7, Issue 2, pp. 238-247. 4.W Zhu et al., Motion-sensor fusion-based gesture recognition and its VLSI architecture design for mobile devices, International Journal of Electronics, 2014, Vol. 101, Issue 5, pp. 621-635.

5.T. Ohguro, et al, 'An 0.18 μm CMOS for mixed digital and analog applications with zero-volt-Vth epitaxial-channel MOSFETs', IEEE Transactions on Electron Devices, vol. 46, no. 7, pp. 1378 - 1383, 2013.

6.Ajay Ogiral et al., Ultra High-Speed and Low-Power Flexible Architecture using State Transition Matrix Model for EPC Gen-2 Communication Protocol Processor, International Journal of Modeling and Simulation, 2012, Vol. 32, Issue 3, pp. 198-205.