# JETIR.ORG ISSN: 2349-5162 | ESTD Year : 2014 | Monthly Issue JOURNAL OF EMERGING TECHNOLOGIES AND INNOVATIVE RESEARCH (JETIR)

An International Scholarly Open Access, Peer-reviewed, Refereed Journal

# Design a Low Power Flash Type ADC with different encoders for high speed applications

S.Pooja, B.Anil kumar

PG. Scholar, Dept of ECE, GMR Institute of Technology, Rajam, Andhra Pradesh, India

Sr. Assistant Professor, Dept. of ECE, GMR Institute of Technology, Rajam, Andhra Pradesh, India

# Abstract

Analog to digital converters (ADC) are extremely important in today's environment. Flash type ADCs are the high speed among the available ADCs. In this paper, the design of Flash ADC structure uses a resistor string to generate reference voltages which are provided to each comparator for comparison with the input voltages. Comparator design is the crucial part of the Flash ADC architecture and used a Cascaded stages CMOS comparator, where each step contributes to boosting gain, sensitivity, and lowering noise of all kinds. One more important part in this ADC is Encoder design; here used a Wallace tree encoder and Heterogeneous encoder in this paper. The designed flash ADC consumes 9.280mW, 53.45ns delay and 11.583mw, 25.39 ns with respect to Wallace tree encoder and Heterogeneous encoder when operated in voltage of 1.2V. The design of A 4-bit flash ADC constructed with 180nm CMOS technology and the results are simulated.

**Keywords:** Flash type ADC; Comparator, Wallace tree and Heterogeneous encoder.

# 1. Introduction

Microelectronic devices and high-end instruments are becoming increasingly sophisticated and capable of performing a wide range of activities with high precision. In nature, real-world signals are analog signals from numerous sources and sensors have values that are constantly changing that can detect movement, temperature, sound, or light, and numerous digital systems monitor analogue signals from these transducers to communicate with their surroundings [4].Whereas Continuous signals are possible and offer an infinite count of possible voltage values, digital circuits only have two distinct states, a logic "1" (HIGH)/ a logic "0" (LOW). As a result, an electrical circuit capable of converting between the two domains of continuous time changing signals to digital signals. Flash ADC is one such simple design utilized for converting continuous time changing signals to digital signals. Flash ADCs are mostly employed in high-speed applications and have a high power consumption. Satellite communication, data gathering, radar processing, and high-density disk storage are all applications for flash ADC.

# 2. Flash ADC architecture

In order to provide an equivalent output code for a specific n-bit resolution, parallel "Flash" A/D converters connect but space out a number of comparators with equal spacing and reference voltages produced by a number of precision resistors. The benefit of parallel converter also called flash converters, has to do with they are simple to develop and no timing clocks are necessary since a reference voltage is used to compare an analog voltage provided to the comparator inputs to [6].

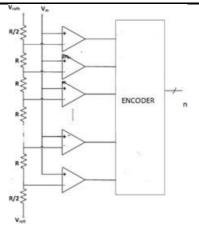

Fig.1. Flash ADC Architecture

N-bit flash ADC is made up of  $2^{N}$  resistors, number of comparators are  $2^{N}$ – 1 and an encoder. At first, the input signal is fed to  $2^{N}$ -1 comparators where N is the resolution in the ADC. For a 4-Bit flash ADC, 16 resistors and 15 comparators are required [7]. Each comparator produced by the resistor strings used in a flash ADC is given a Vref. The resistor string circuit is employed for generate reference voltage which is used as one of the inputs to the comparator. Here reference voltage, which is produced from resistor ladder circuit as it descends from top to bottom because voltage decreases across the resistor. The voltage divider network arrangement yields V<sub>RF</sub> using equivalent resistors. For example, the Vref level is certainly equal to half of the supply voltage or V/2, if the two resistors have equal values, or if R1 = R2. An analog comparator has two analog inputs that is applicable to contrast two distinct voltage (V<sub>IN</sub>) signal, and the other receives a reference voltage (V<sub>REF</sub>). Two levels of voltages are compared at the comparator's input is made to choose one of two possible states for the comparator's digital logic output: "1" or a "0" [9]. The output of the comparator is the thermometer code. The thermometer code is then altered into binary code by the  $2^{N}$ – 1 to N encoder [10]. A combinational circuit known as an encoder transforms binary data from 2N input lines into N output lines, which represent the input's N bit code.

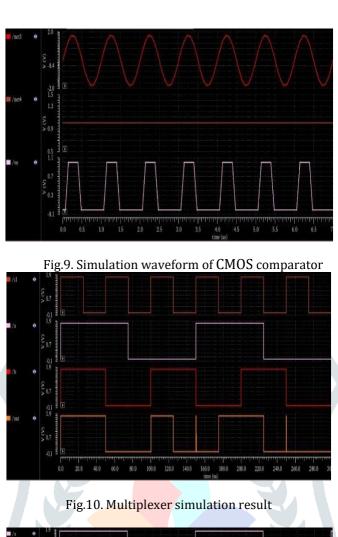

#### 1.1. Comparator:

The schematic diagram of the comparator, which converts input voltage to logic 1/0, is the ADC architecture's most essential element. The voltage comparators evaluate the variation between the input and reference voltages. generated from the resistor string.

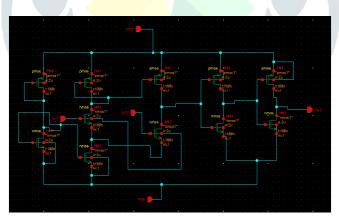

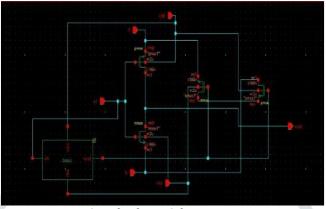

Figure .2. Schimatic Diagram of CMOS Comparator

There are plenty other comparators available, including discrete, RDC (Resistor Driving Comparator), open loop, differential, Domino logic, and pseudo dynamic latched comparators. However, for high-speed applications, Flash ADC needs a comparator with high sensitivity, gain, and low power consumption. A CMOS comparator with cascaded stages was employed here, and with each stage, both gain and sensitivity increased as the noise levels decreased. The output of the pre-amplifier stage, which is the first step, is fed into the decision stage's input. The decision-making stage is

followed by the post-amplifier stage.  $V_{REF}$ , the reference voltage is compared to  $V_{IN}$  that is used to the other input. The comparator output is "OFF" if the input voltage falls below the reference voltage ( $V_{IN} < V_{REF}$ ), and "ON" if the input voltage exceeds the reference voltage ( $V_{IN} > V_{REF}$ ). Result is, the comparator compares the two voltage levels and determines which is greater.

#### 1.2. Wallace tree encoder:

This encoder block is essential to obtain the accurate the applied binary values analog input signal. It changes a sequence of 0s and 1s from comparators to binary format. The combinational circuit known as the encoder transforms binary information from 2N input lines are converted into N output lines, representing N bit code for the input. It is expected that there is only one active one input line at a time for straightforward encoders.

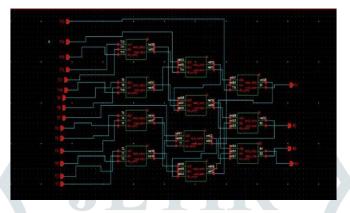

Fig.3. Schematic Diagram of Wallace tree encoder

This paper contains the encoder is carried out employing the Wallace tree design, which includes full adders. The equation gives the number of complete adder cells required to create an N bit encoder,

$$X_N = \sum_{i=1}^{N} (i-1)2^{(N-1)}$$

As a result of the quantity of ones and it is also referred to as a one's counter and provides binary output in compliance. This encoder turns comparator output into accurate binary output even when bubble faults are present. The Wallace tree encoder uses less electricity than a ROM-based encoder. Another benefit of this encoder is that the propagation delay is equal because all inputs pass through an equal amount of complete adders. It is also flexible and generates positive results for any settlement.

Full Adder:

Here designed a full adder with the help of 2:1 Multiplexers.

Fig.4. Schematic Diagram of Full Adder

#### 1.2.1.1. Multiplexer:

A circuit called a multiplexer that combines 2<sup>n</sup> input lines with only one output line. A multiplexer serves as a combinational circuit with a lot of inputs and one output. The output line receives and transmits binary data that is received based on the input lines. According to the selection line values, it will be connected to the output by one of these data inputs. In this project, a 2:1 multiplexer is used. In the 2:1 mux, there are only two inputs and a single output. Based on a variety of inputs which attend to the selection line S, It will be connected to the output from one of these two inputs. We know that multiplexer is also called a data selector. Here, the Multiplexer is designed with Modified GDI (Gate Diffusion Input) logic.

Fig.5. Multiplexer Schematic Diagram

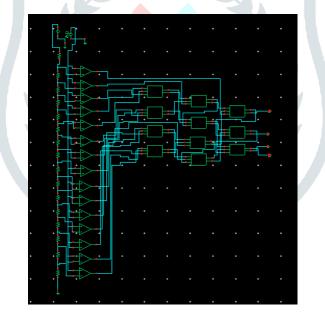

#### 1.3. Heterogeneous encoder

Any existing encoder, such as the Wallace tree encoder or the Fat tree encoder, can be used to construct a heterogeneous encoder. Seven multiplexers, two inverters, and four complete adders make up the heterogeneous encoder. Actually, we can't give input directly to the output in cadence virtuoso. So, two inverters used in the circuit. Wecan use buffer circuit in place of two inverters. Also, two cascaded inverters act as buffer circuit. The inputs to the encoder are 15 (T1 – T15) and it produces 4 outputs (B4-B1). This can tolerate bubble errors and allow the remaining signals to serve as inputs. The Wallace encoder is likewise without of bubble error, although circuit is complicated. As a result the heterogeneous encoder is simple to implement and usage a little power.

Fig.6. schematic diagram of heterogeneous encoder

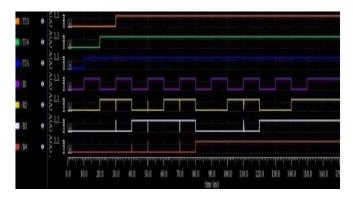

Fig.7. simulated waveforms of heterogeneous encoder

#### 1.4. Flash ADC:

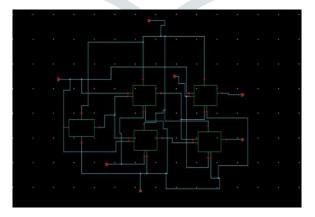

Finally Designed the Flash ADC architecture with a two-stage CMOS comparator and two types of encoders (Wallace Tree Encoder and heterogeneous encoder). The reference input voltage is sent to the inverting pins of comparators, even though analog the input signal is sent to the comparator's non-inverting pin. The comparator compares both inputs and outputs the results in the form of 1s and 0s. If the input voltage exceeds the reference voltage, then the output of the comparator is 1. If the input voltage is less than the reference voltage, then the output of the comparator is 0. The set of 1's & 0's is called thermometer code. Here one thermometer to binary code converter is needed. So, the Wallace Tree encoder is used for that conversion. The encoder output is in the form of binary and this output is called a digital output.

Fig.8. Schematic Diagram of Flash ADC

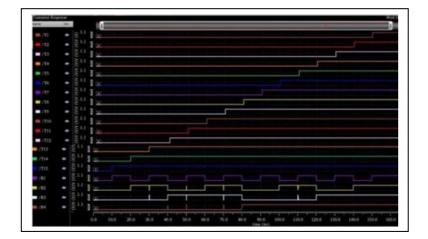

- 2. Result

- S

Fig.11. Full Adder Simulation result

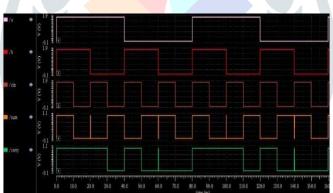

Fig.12. Simulation waveforms of Wallace Tree Encoder

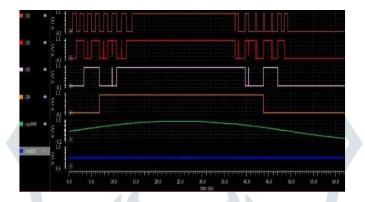

Fig.13. Simulation results of Flash ADC

| Parameters        | ADC with Wallace tree  | ADC with Heterogeneous encoder |

|-------------------|------------------------|--------------------------------|

| Vdd (V)           | 1.2                    | 1.2                            |

| Technology        | 180nm                  | 180nm                          |

| Resolution        | 4-bit                  | 4-bit                          |

| Frequency         | 10 MHz                 | 10 MHz                         |

| Delay             | 53.45 <mark>ns</mark>  | 25.39 ns                       |

| Power consumption | 9.280 m <mark>W</mark> | 11.583 mW                      |

Table 1: Flash ADC Comparison

# 3. Conclusion

This paper designed a flash ADC with Wallace tree-based encoder or heterogeneous encoder, CMOS comparator with cascaded stages, and string of resistive ladder network. Designed circuit is 180nm CMOS technology was used to simulate. This ADC's has the significant advantages with low power usage and short latency. When this ADC designed with Wallace tree encoder, we observe the 9.280 mW power consumption, 53.45 ns delay and ADC with heterogeneous encoder design has 11.583 mW, 25.39 ns. Both circuits operated as input of 1.2V at a frequency of 10MHz. The Flash ADC created can be used in high-speed applications.

## References

[1] Ashima Gupta, Anil Singh, Alpana Agarwal,

"Highly-digital voltage scalable 4-bit flash ADC", IET Circuits, Devices & Systems, Volume: 13, Issue: 1, 1 2019.

- [2] Jayakumar A, Vishnu K. A 7-bit 500-MHz flash ADC. First International Conference on Computational Systems and Communications (ICCSC), Trivandrum; 2014. p. 75–79 <u>https://doi.org/10.1109/COMPSC.2014.7032624</u>.

- [3] Mukherjee S, Dutta A, Roy S, Sarkar CK. Implementation of low power programmable flash ADC using IDUDGMOSFET, IEEE Transactions on Circuits and Systems II: Express Briefs. 2018; 65(7):844–48 https://doi. org/10.1109/TCSII.2017.2728619.

- [4] Disha Gaude, Bathini Poornima, K.M. Sudharshan and Prashant V. Joshi, "Design and Simulation of 4-Bit Flash Analog to Digital Converter (ADC) for High Speed Applications", Indian Journal of Science and Technology, Vol 12(36), September 2019.

- [5] Prof. Jayashree C Nidagundi, Sunita S Bettakusugal, "Design and Implementation of 3-Bit Flash Analog to Digital Converter (ADC)", International Journal of Latest Trends in Engineering and Technology, Volume-10, Issue-3, pp.208-214, 2018.

- [6] Chanakya Dharani, Ravi.J, "TIQ Flash ADC Design using a Low Power Multiplier Based Encoder", International Journal of Recent Technology and Engineering (IJRTE) ISSN: 2277-3878, Volume-8, Issue-2S2, July 2019.

- [7] D. S. Shylu Sam, P. Sam Paul, Diana Jeba Jingle, P. Mano Paul, Judith Samuel, J. Reshma, P. Sarah Sudeepa, G. Evangeline (2021). "Design of Low-power 4-bit Flash ADC Using Multiplexer Based Encoder in 90nm CMOS Process", INTL JOURNAL OF ELECTRONICS AND TELECOMMUNICATIONS,2022, VOL. 68, NO. 3, PP. 565-570 Manuscript received May 23, 2021.

- [8] Piyush Kumar, "Low-Power Heterogeneous Encoder Based 4-Bit Flash ADC Using TIQ", International Journal of Electrical and Electronics Research, ISSN 2348-6988 (online) Vol. 3, Issue 2, pp: (662-669), Month: April - June 2015.

- [9] Patil H, Raghavendra M. Low power dynamic comparator for 4 bit Flash ADC. IEEE International Conference on Computational Intelligence and Computing Research (ICCIC), Chennai; 2016. p. 1–4. https://doi.org/10.1109/ ICCIC.2016.7919550.

- [10] Nirali Hemant Patel , "Power Efficient 4-bit Flash ADC using Cadence Virtuoso", International Journal of Engineering Research & Technology (IJERT) ISSN: 2278-0181, Vol. 10 Issue 03, March-2021.

- [11] Disha Gaude, Bathini Poornima, K.M. Sudharshan and Prashant V. Joshi, "Design and Simulation of 4-Bit Flash Analog to Digital Converter (ADC) for High Speed Applications", Indian Journal of Science and Technology, Vol 12(36), September 2019.

- [12] Marcel Siadjine Njinowa, Hung Tien Bui, François-Raymond Boyer, "Design of low power 4-bit flash ADC based on standard cells", New Circuits and Systems Conference (NEWCAS), DOI: 10.1109/NEWCAS.2013.6573626, IEEE 2013.

- [13] Titu Mary Ignatius, Jobin.K.Antony, Silpa Rose Mary, "Implementation of High Performance Dynamic Flash ADC", International Conference on Magnetics, Machines & Drives, DOI: 10.1109/AICERA.2014.6908268, 2014.

- [14] Abhijith N, Dr. Jayanthi K Murthy, "Design and Implementation of First Two Stages of HFB ADC using Cadence Virtuoso Tool", International Journal of Engineering Research & Technology (IJERT) ISSN: 2278-018, Vol. 4 Issue 07, July-2015.

- [15] Biswas S, Kumar Das J, Prasad R. Design and Implementation of 4 Bit Flash ADC Using Low Power Low Offset Dynamic Comparator. International Conference on Electrical, Electronics, Signal, Communication and Optimization; 2015. p. 1–6. https://doi.org/10.1109/EESC0.2015.7253935.

- [16] Panchal S D1, Dr. S S Gajre2, Prof. V P Ghanwat, "Design and implementation of 4-bit flash ADC using folding technique in cadence tool", International Journal of Advanced Research in Computer and Communication Engineering, Vol. 1, Issue 4, June 2012.

- [17] Kalita, T., Das, B.: 'A 4 bit quantum voltage comparator based flash ADC for low noise applications'. 2016 Conf. Emerging Devices and Smart Systems (ICEDSS), Namakkal, 2016, pp. 24–29.

- [18] Moyal, V., Tripathi, N.: 'Adiabatic threshold inverter quantizer for a 3-bit flash ADC'. 2016 Int. Conf. Wireless Communications, Signal Processing and Networking (WiSPNET), Chennai, 2016, pp. 1543–1546.

- [19] Deepali Koppad, Sujatha Hiremath "Low Power 1-Bit Full Adder Circuit Using Modified Gate Diffusion Input (GDI)" conference on First International micro and nano technologies.

## © 2023 JETIR August 2023, Volume 10, Issue 8

- [20] Anshul Jain, Abul Hassan" Design of Low power multiplexers using different Logics" International Journal of Science, Technology, and management Vol-4.

- [21] Pereira, P., Fernandes, J.R., Silva, M.M.: 'Wallace tree encoding in folding and interpolation ADCs'. IEEE Int. Symp. Circuits and Systems, May 2002, vol. 1, pp. 509–512.

- [22] Behzad Razavi, Design of Analog CMOS Integrated Circuits, 2<sup>nd</sup> Edition, McGraw-Hill, 2017. (<u>https://electrovolt.ir/wp-content/uploads/2014/08/Design-of-Analog-CMOS-Integrated-Circuit-2nd-Edition-ElectroVolt.ir\_.pdf</u>).

- [23] Tony Chan Carusone, David Johns, Kenneth Martin: Analog Integrated Circuit Design, 2<sup>nd</sup> Edition, John Willy Publications, 2011.(<u>http://fa.ee.sut.ac.ir/Downloads/AcademicStaff/16/Courses/87/[Tony Chan Carusone; David Johns; Kenneth W Martin(BookZZ.org)-Book2011.pdf</u>).

- [24] Rudy V, dePlassche, CMOS Integrated ADCs and DACs, Springer, Indian Edition, 2005.(<u>https://www.springer.com/gp/book/9781402075001</u>).