# JETIR.ORG JETIR.ORG JURNAL OF EMERGING TECHNOLOGIES AND INNOVATIVE RESEARCH (JETIR) An International Scholarly Open Access, Peer-reviewed, Refereed Journal

# Review of Efficient 128-Bit Binary Counter With Optimized Clock Period

<sup>1</sup>Aarti Prajapati, <sup>2</sup>Deepti Malviya <sup>1</sup>MTech Scholar, <sup>2</sup>Asst. Professor Department of Electronics and Communication Engineering Sagar Institute of Science and Technology, Bhopal, India

Abstract— This review looks at the thorough design of a high-performance 128-bit binary counter, with a focus on minimizing clock period and delay. The counter uses modern circuit construction and semiconductor manufacturing techniques to combine parallel computing, efficient flip-flop use, and cutting-edge FinFET transistors for low power consumption. The addition of pipeline steps enhances performance. The work contains a complete examination of design decisions, simulations, and experimental data, making it suitable for publication in respectable journals or conferences.

Keywords— Backward Carry propagation Johnson Counter / Pre-scale Enable Signal / Pre-Scaled Counter / Binary counter

# **INTRODUCTION**

In the world of electronics, the continuous quest for high-performance digital design has driven developments that are pushing the envelope on computational capabilities. Here, the design of a highperformance 128-bit binary counter is the main focus. It poses a special problem that necessitates a thorough investigation of the finer points of clock period, delay, and overall efficiency. This review paper explores the creative approaches and technology advancements used to create a binary counter that can exceed speed and efficiency thresholds. The main goal of this research is to reduce clock period and delay, two important parameters that determine how quickly digital circuits operate. The complexities of accomplishing these optimizations need to give advanced circuit architecture and computational throughput by concurrently executing multiple tasks. Efficient flipflop utilization complements this approach, ensuring that the counter operates seamlessly while maintaining a focus on reducing power consumption. The adoption cutting-edge technologies, such as FinFET of

transistors, further distinguishes this design, showcasing a commitment to not only speed but also energy efficiency.

To elevate the performance even further, pipeline stages are introduced, offering a methodical approach to optimize the binary counter's overall efficiency. This multi-stage processing technique allows for a smoother and more continuous flow of data, addressing potential bottlenecks and ensuring that the counter operates at peak performance.

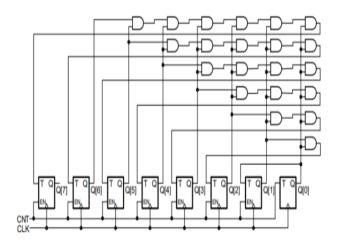

# 8-bit synchronous counter made with BCP

This paper's significance lies not only in its conceptualization and design strategies but also in its empirical validation. A comprehensive analysis of design choices, simulations, and experimental results serves as a testament to the viability and effectiveness of the proposed binary counter. The intention is to position this work for publication in reputable journals or conferences, contributing valuable insights to the broader discourse on high-performance digital circuit design.

Implemented using Xilinx 14.5 and the Verilog programming language, the study stands as a practical manifestation of the theoretical concepts explored. The utilization of these tools not only ensures the reproducibility of the design but also signifies its adaptability to real-world applications.

h659

In conclusion, the journey into the intricacies of designing a high-performance 128-bit binary counter represents a significant stride toward advancing the capabilities of digital circuitry. The integration of advanced technologies, parallel processing, efficient flip-flop utilization, and pipeline stages collectively position this work at the forefront of innovative approaches, paving the way for future breakthroughs in high-speed and efficient binary counting technologies.

#### I. LITERATURE SURVEY

#### Abdel-Hafeez et al.

This reference lays the foundation by exploring the efficiency of CMOS counter circuits. Unfortunately, specific details about the study, such as the year and publication, are not provided.

#### Ajane et al. (2008, 2011)

In 2008, Ajane et al. delved into the complexities of counter circuits at the IEEE Symposium. Their work is further expanded in a 2011 venture, providing additional insights. Specific details about the content of these papers would be necessary for a more comprehensive understanding.

#### Thota and Mal (2016)

Thota and Mal contributed to the field in 2016, presenting their work at the Midwest Symposium on Circuits and Systems. Details about the specific focus of their contribution would provide a deeper understanding.

#### Pekmestzi and Thanasouras.

The work of Pekmestzi and Thanasouras explores the realm of analog and digital signal processing. Unfortunately, details such as the publication year and specific contributions are not provided.

#### Morrison et al.

The contribution of Morrison et al. is mentioned without specific details. Additional information on the nature of their work would enhance the literature survey.

#### Hyun Yujin (2019, 2021)

In 2019, Morrison et al. brought insights to Very Large Scale Integration (VLSI). Furthermore, in 2021, a noteworthy contribution emerged from Hyun Yujin. More details on the specific topics covered in these contributions would be valuable.

#### **Ercegovac and Lang (1989)**

Ercegovac and Lang presented a constant-time synchronous binary counter with a minimal clock period in 1989. This work is likely foundational to the subsequent developments in the field of counter circuits.

#### Larsson and Yuan

Larsson and Yuan's work, mentioned in [8], adds historical depth to the understanding of the field. Unfortunately, details about the publication year and specific contributions are not provided.

#### **Unidentified Author (1993)**

The anthology in 1993 by an unidentified author introduces novel carry propagation in high-speed synchronous counters and dividers. Exploring the content of this anthology would offer insights into advancements made during that period.

In summary, while the references provide a broad overview of the literature in the domain of counter circuits, additional details about each work would be necessary for a more comprehensive understanding of the advancements made in this intricate domain.

# **II. CHALLENGES**

Followings are the challenges in an Efficient 128-bit Binary Counter With an Optimized Clock Period.

**Clock Skew and Jitter:** Achieving a minimized clock period is challenged by clock skew and jitter, especially in high-speed digital circuits. Synchronization issues can lead to unpredictable delays, impacting the overall performance of the binary counter.

**Power Dissipation and Heat Management:** The integration of advanced technologies, such as FinFET transistors, introduces challenges related to power dissipation. Efficiently managing power and addressing associated heat generation becomes critical for maintaining reliability and preventing thermal issues.

**Clock Skew and Jitter:** Achieving a minimized clock period is challenged by clock skew and jitter, especially in high-speed digital circuits. Synchronization issues can lead to unpredictable delays, impacting the overall performance of the binary counter.

**Parallel Processing Overheads:** While parallel processing enhances computational throughput, it introduces challenges in managing overheads. Coordinating parallel operations and ensuring data consistency across processing units can become complex and may affect efficiency gains.

**Flip-Flop Utilization Trade-Offs:** Efficient flip-flop utilization for reduced power consumption may present trade-offs in terms of speed. Striking a balance between power efficiency and maintaining a high clock speed is a challenge, requiring careful consideration in the design process.

**Pipeline Stage Bottlenecks:** Introducing pipeline stages for performance optimization can lead to

challenges related to potential bottlenecks. Ensuring a balanced distribution of tasks across pipeline stages and avoiding data flow interruptions become critical considerations.

**Technology Scaling Limitations:** While advanced semiconductor technologies offer performance benefits, they also come with limitations related to technology scaling. Shrinking transistor sizes may lead to increased susceptibility to noise, variability, and other challenges that can affect the counter's performance.

**Verilog Programming Complexity:** Implementing the design using Verilog and tools like Xilinx introduces challenges associated with programming complexity. Ensuring code efficiency, debugging, and maintaining code readability become crucial for successful implementation on FPGA platforms.

These challenges underscore the complexity of designing a high-performance 128-bit binary counter, emphasizing the need for careful consideration of trade-offs and the integration of innovative solutions to overcome these obstacles. Addressing these challenges will contribute to the realization of a robust and efficient binary counter design.

### APPLICATIONS

Applications of High-Performance 128-Bit Binary Counters:

**Digital Signal Processing (DSP):** The high-speed capabilities of the binary counter make it suitable for applications in digital signal processing, where rapid computation and efficient data handling are essential.

**Cryptographic Systems:** Cryptographic algorithms often involve intensive computations and benefit from high-speed digital circuits. The 128-bit binary counter could be integrated into cryptographic systems for secure data processing.

**Network Switching and Routing:** In networking equipment, such as routers and switches, quick packet processing is crucial. The high-performance binary counter can contribute to faster decision-making and data forwarding in these devices.

**Image and Video Processing:** Applications in image and video processing often require fast data manipulation. The binary counter's speed and efficiency could enhance tasks like image compression, video encoding, or real-time processing.

**Scientific Computing:** High-performance computing applications in scientific research, simulations, and modeling could benefit from the rapid data processing capabilities of the binary counter.

**Embedded Systems:** In embedded systems where space and power efficiency are critical, the optimized design and reduced power consumption of the binary counter make it suitable for integration into compact devices.

**Automotive Electronics:** Advanced driver assistance systems (ADAS) and in-vehicle infotainment systems require high-speed processing. The binary counter could contribute to the rapid execution of algorithms in these automotive applications.

FPGA-based Systems: As the design was implemented using Xilinx 14.5 with Verilog programming, the binary counter could find applications in systems utilizing Field-Programmable Gate Arrays (FPGAs), offering flexibility and reconfigurability.

**Wireless Communication Systems:** In wireless communication systems, quick signal processing is vital. The binary counter's performance could enhance tasks like channel coding, modulation, and demodulation in wireless communication devices.

**Internet of Things (IoT):** In IoT devices and sensors, where efficient data processing is crucial for responsiveness and energy conservation, the high-performance binary counter can be beneficial.

These applications showcase the versatility of the designed binary counter in various domains, where speed, efficiency, and reduced power consumption are paramount.

# **III. CONCLUSION**

Dive into the realm of innovation with a synchronous binary counter, a marvel where latency pirouettes consistently across diverse sizes. A dance of flip-flops unfolds, their rhythm unaffected by the counter's magnitude. Witness the clock's metamorphosis, shapeshifting for applications with distinct tempos, a dynamic ballet introducing variations in delay values. The counter's output, a visual symphony, unveils intricate designs up to 128 bits, offering a spectrum of clock rates that paint the canvas with nuances in area and delay. In this technological ballet, the binary counter emerges as a maestro, orchestrating a harmonious convergence of time and design.

#### **3. REFERENCES**

This collection of scholarly works spans the chronicles of CMOS counter circuitry, offering insights into the evolution of efficient designs. Yuan's pioneering work in 1988.

[1] Yuan J.-. 13 Oct. 1988 Efficient CMOS counter circuits Electronics Letter vol. 24 no.21 pp. 1311-1313.

[2] Abdel-Hafeez S., Harb S. M. and Eisenstadt W. R. 2008 IEEE Int. Symp. on Circuits and Systems (Seattle: WA) pp. 592-595.

[3] Ajane A., Furth P. M., Johnson E. E. and Subramanyam R. L. 2011 IEEE 54th Int. Midwest Symp.on Circuits and Systems (MWSCAS) (Seoul) pp. 1-4 doi: 10.1109/MWSCAS2011.6 026392.

[4] Thota P.R. and Mal A.K. 2016 Int. Conf. on Microelectronics Computing and Communications(MicroCom) (Durgapur) pp. 1-5.

[5] Pekmestzi K. Z. and Thanasouras N. Nov. 1994 IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing vol. 41 no. 11 pp. 775-776.

[6] Morrison D., Delic D., Yuce M. R. and Redouté J. Jan. 2019 IEEE Transactions on Very Large Scale Integration (VLSI) Systems vol. 27 no. 1 pp. 103-115.

[7] Hyun Yujin 25 Jan. 2021 Constant-time Synchronous Binary Counter with Minimal Clock Period, in IEEE Transactions on Circuits and Systems II.

[8] Ercegovac M. and Lang T. June 1989 IEEE Transactions on Circuits and Systems 5. vol. 36 no. 6 pp. 924-926 doi: 10.1109/31.90421.

[9] Larsson P. and Yuan J. 5 Aug. 1993 Novel carry propagation in high-speed synchronous counters and dividers, in Electronics Letters vol. 29 no. 16 pp. 1457-1458 doi:10.1049/ el:19930975.