# JETIR.ORG ISSN: 2349-5162 | ESTD Year : 2014 | Monthly Issue JOURNAL OF EMERGING TECHNOLOGIES AND INNOVATIVE RESEARCH (JETIR)

An International Scholarly Open Access, Peer-reviewed, Refereed Journal

# DESIGN OF TWO INTERLEAVED ERROR DETECTION AND CORRECTION USING HSIAO CODE AND CRC

# <sup>1</sup>Gajarao Roop Kumar, <sup>2</sup>Hanumanthu Sruthi,

<sup>3</sup>Kathi Cherishma, <sup>4</sup>Katari Sunil Kumar, <sup>5</sup>Chebrolu Praveen Kumar

- <sup>1</sup>UG Student Department of ECE, PBR VITS, India,

- <sup>2</sup> UG Student Department of ECE, PBR VITS, India,

- <sup>3</sup> UG Student Department of ECE, PBR VITS, India,

- <sup>4</sup> UG Student Department of ECE, PBR VITS, India,

- <sup>5</sup> UG Student Department of ECE, PBR VITS, India,

**Abstract:** A radiation-induced single-event upset (SEU) is a major disruption to electronics operating in satellites. If not rectified, a single-bit-error can become uncorrectable. There are several methods like Forward Error Correction Codes, Error Correction Codes, hamming codes, and many more from these methods, individual HSIAO, CRC, Hamming, BCH are used for error correction & detection. This project, presents two interleaved Double-Adjacent-Error Corrections (DAECs) for Error Detection and Correction (EDAC), using the Hsiao Code and Cyclic Redundancy Code (CRC). In this design single-bit-error, double-adjacent-bit-errors can be corrected and double bit-errors up to four-adjacent-bit-errors can be detected and corrected. The Hsiao Code EDAC has the best performance for speed, hardware requirement, and three- and four-bit-error detection. Its higher three- and four-bit error detection rates reduce the probability of an erroneous EDAC correction. The Hsiao code EDAC encoder design requires less bit – weight than the CRC EDAC, in contrast, has a higher error detection rate for both three- and four-bit errors. We used Verilog HDL and Xilinx Vivado to create and simulate designs.

## Index Terms - Hsiao Code, CRC, Hamming Code, BCH, EDAC

## I. INTRODUCTION

As a semiconductor's geometry gets smaller, the probability of a bit inversion in memory devices induced by external influences, such as an electrical surge and ionizing radiation increases. These anomalies interrupt the regular operation of an electronic device, causing mission failures. An Error Detection and Correction (EDAC) design mitigates these anomalies by detecting and correcting any bit inversions in memory devices such as the static memory (SRAM and SSRAM), and dynamic memory (SDRAM and DRAM). A safety-critical, fault-tolerant system requires a stringent specification for its EDACs, with minimizing erroneous correction rate as the goal. There are several prominent single error correction and double error detection (SEC-DED) EDACs proposed, such as the Hamming, Bose– Chaudhuri– Hocquenghem (BCH), and Hsiao Codes.

Error correcting codes have been widely applied to computer memory systems to enhance reliability. In particular, single bit error correcting and double bit error detecting (SEC-DED) codes have been successfully used in semiconductor memory systems organized in a one-bit-per-chip manner. This is because any failure in one chip can corrupt, at most, one bit per codeword in such systems. Recently, some systems adopt a b-bit-per-chip organization, where  $b \ge 2$ . A chip failure in these systems causes the word read-out to have a b-bit block, called b-bit byte or simply byte, in error. Therefore, single b-bit byte error sand detecting double b bit byte errors, have found applications in this kind of systems.

Among the predominant errors, however, are soft errors induced by D particles, which are said to be apt to manifest themselves as random bit errors still in byte organized systems. Cell failures also result in random bit errors. Therefore, designers of error control codes for byte organized memory systems should take into account two types of errors, byte errors and bit errors. Strictly speaking, bit errors are a class of byte errors which corrupt exactly one bit within a 2 byte, but we refer to such errors as bit errors, and the others as byte errors here. Since the vast majority of the errors in these systems are random bit errors, which may be caused by D particles or cell failures, it is more likely that a random bit error occurs lined up in a codeword with another existing byte error due to a chip failure than the case where as many as two chips fail to yield a double byte error. We refer to such an error, i.e., an error which corrupts both one byte and one bit in another byte, as a single byte plus single bit error

hereafter. In other words, single byte plus single bit errors are double byte errors such that at least one of the two-byte errors has Hamming weight one.

To improve the reliability of computer memories error correcting and/or error detecting codes have been commonly used. As the LSI technology moves towards higher levels of integration and packaging density the current bit-per-card organization may not be practical from a packaging and memory capacity standpoint and byte-per-card organization may become the general practice. In circuits with such an organization, physical failures will lead to bit as well as byte errors. The general situation with memories using byte-per-card organization. Though each card or circuit is shown to be b bits wide it is possible to have cards of different sizes. However, in this correspondence, for the sake of simplicity, let assume that all cards are b bits wide and it will refer to the collection of b bits as a byte. Depending on the location of a fault, a fault in a card may affect a single bit (these are called failures bit errors) or more than one bit in a byte (these are called failures byte errors). Known codes do not exist for correction and/or detection of several classes of potential failures in byte-per card organized digital systems. For example, in one application (involving a memory system) codes to correct single bit errors and detect single byte errors were required.

Certain known codes which correct both the bit and the byte errors could have been used but these codes would have required higher redundancy. In this correspondence we will derive a class of linear binary error-correcting codes to correct single bit errors and simultaneously detect single byte errors and double bit errors. The research work carried out here provided an insight into the development of error detection and correction systems. The research area of the Internet of Things in recent years has experienced growth and development in an interdisciplinary manner.

### **II. LITERATURE SURVEY**

Babitha and Divya's single error correction, double error detection, double adjacent error correction, and triple adjacent error detection (SEC-DED-DAEC-TAED) EDAC used a modified Hamming Code. The state of the EDAC could not be verified since no validation results were presented. Jun and Lee proposed an SEC-DED-DAEC EDAC that requires the least redundancy bits relative to the other EDACs in their work. One limitation of having reduced redundancy bits is that the percentage of erroneous corrections is very high for the three- and four-bit-errors-there was no data to support the three- and four-bit-error detection capabilities. Hsiao proposed a class of optimal minimum odd-weighted column SEC-DED code known as the Hsiao Code [1] in the 1970s to improve the speed, cost, and reliability of the decoding logic.

Although several proposed SEC-DED EDACs exist in the literature, the Hsiao Code remains the most optimized SEC-DED EDAC. Others proposed various classes of SEC-DED codes, that can detect any number of errors in a single byte. These codes are known as single-error-correction double-error detection single-byte-error-detection (SEC-DED-SBD) codes. An EDAC with a double-error-correction and triple error-detection code may be used, at the cost of higher overhead of check-bits and more sophisticated hardware to implement the error correction and detection. This type of implementation may result in a slower EDAC that is not suitable in a high-performance system.

## **III. EXISTING METHOLOGY**

In the existing method, individual Hsiao Code, CRC, Hamming, BCH are used for error correction & detection. the three Hsiao Code's rules and show how we can use them to create our Hsiao Code's EDAC H-matrix:

1. Every column should have an odd number of 1's; i.e., all column vectors are of odd-weights.

2. The total number of 1's in the H-matrix should be at a minimum.

3. The number of 1's in each row of the H-matrix should be made equal, or as close as possible, to the average number, i.e., the

total number of 1's in the H-matrix divided by the number of rows.

Cyclic Redundancy Codes (CRCs) are conventional methods for error detection in networking and other applications. For networking, the interest is the Hamming Distance (HD), which is the least possible number of bit inversions in a message that can create an error undetectable by that message's CRC-based Frame Check Sequence. For example, if a CRC polynomial has an HD of 6 for a given network, all possible combinations of 1- to 5-bit errors (where a bit error is an inversion of a bit value) will be detected. At least one combination of 6 bits that, when corrupted within a message, is undetectable by that CRC.

## IV. DISADVANTAGES OF EXISTING METHOLOGY

- Area efficiency is very less

- Error correcting and detecting rate is very low

- Performance is low

### V. PROPOSED METHOLOGY

#### A. DESIGN OF HSIAO CODE'S ENCODER MATRIX

The Hsiao Code implementation is straightforward. However, balancing the Hsiao Code's encoder matrix (also called the H-matrix) rows' bit-weights by hand is not an easy task. Instead, we created a C++ program, a Hsiao Code's matrix generator, to generate the H-matrices compliant with the three Hsiao Code's rules. We also created

another C++ program, a code generator, to take the generated matrix as the input and produce the Verilog code for the EDAC's encoder.

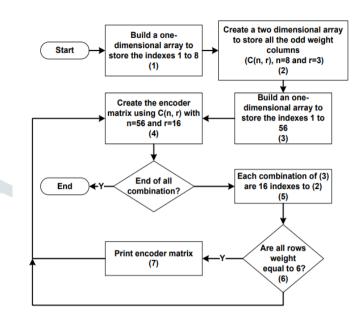

Fig. 1: Hsiao Code Encoder Matrix Generator

In the following, we introduce the three Hsiao Code's rules and show how we can use them to create our Hsiao Code's EDAC H-matrix:

1. Every column should have an odd number of 1's; i.e., all column vectors are of odd-weights. In the following, we use n to indicate the number of rows in the H-matrix, and r to indicate the number of 1's in each column, which must be an odd number.

use the combination formula C (n, r) = ((n!)/(r!(n-r)!)) to generate all possible odd-weighted columns.

- 2. The total number of 1's in the H-matrix should be at a minimum.

- 3. The number of 1's in each row of the H-matrix should be made equal, or as close as possible, to the average number, i.e., the total number of 1's in the H-matrix divided by the number of rows.

Based on the rules the rules above, we can design matrix generator in C++. Fig. 2 shows the flowchart of our generator.

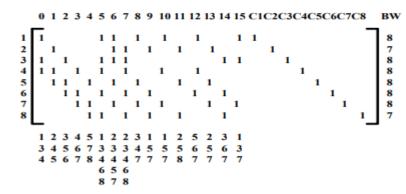

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 C1 C2 C3 C4 C5 C6 C7C8 BW 7 5 7 1 1 1 1 1 1 3 2 3 3 3 2 5 5 6 5 2 2 4 2 3 2 4 4 4 4 7 6 6 4567856786 8 7 8

Fig. 2: This diagram shows the Hsiao Code's encoder matrix generated by the matrix generator.

#### **B. DESIGN OF A CYCLIC REDUNDANCY CODE'S ENCODER MATRIX**

Cyclic Redundancy Codes (CRCs) are conventional methods for error detection in networking and other applications. For networking, the interest is the Hamming Distance (HD), which is the least possible number of bit inversions in a message that can create an error undetectable by that message's CRC-based Frame Check Sequence. For example, if a CRC polynomial has an HD of 6 for a given network, all possible combinations of 1- to 5-bit errors (where a bit error is an inversion of a bit value) will be detected. At least one combination of 6 bits that, when corrupted within a message, is undetectable by that CRC.

We design our next EDAC based on a CRC polynomial to leverage the CRC detection capability. To increase the information rate, we compute the 16-bit message with an 8-bit CRC generator. To reduce the bit-weight in the encoder matrix, we set the CRC's seed value to zero. When a two-input XOR gate has an input equal to a logical zero, its output value is equal to the other input's value. Based on this Boolean state, we eliminate the XOR gates required for the seed value, thus reducing the bit-weight of our CRC matrix. We developed a CRC-based encoder matrix generator in C++ to generate our EDAC encoder matrix with these criteria.

Fig. 3: this diagram shows the CRC's EDAC encoder matrix generated by our CRC matrix generator with polynomial =  $x^8 + x^3 + x^2 + 1$ .

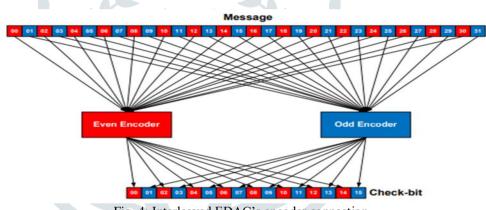

#### C. Design an interleaved EDAC

Fig. 3 shows the architecture of our interleaved EDAC encoder design. Our EDAC uses two identical single error correction and double error detection (SEC-DED) EDACs configured as the even and odd encoders, syndromes, and decoders. For example, two Hsiao Code encoder matrices generated, or two CRC encoder matrices generated in can be used in Fig. 3. As the two identical encoders. This configuration improves the error correction and detection rates. For example, if a double-bit error has one error occurring on an even-bit, and the other on an odd-bit of a codeword, this error can be corrected. Verilog code of the interleaved even and odd encoders, an equivalent to the diagram shown in Fig. 3.

Fig. 4: Interleaved EDAC's encoder connection

EDAC uses two identical single error correction and double error detection (SEC-DED) EDACs configured as the even and odd encoders, syndromes, and decoders. For example, two Hsiao Code encoder matrices generated in existing, or two CRC encoder matrices generated in existing can be used in Fig. 8 as the two identical encoders. This configuration improves the error correction and detection rates. For example, if a double-bit error has one error occurring on an even-bit, and the other on an odd-bit of a codeword, this error can be corrected. In this proposed method is a combination of Hsiao code and CRC. By combining both the methods with the help of interleaving process. Fig. 12 shows the error detection and correction metrics of our EDAC designs (Hsiao Code and CRC). Our EDACs can correct all single-bit-errors. For double-bit-errors, our EDACs can correct all the double-adjacent-bit-errors. Additionally, double-bit-errors have one error occurring on an even-bit and the other on an odd-bit of a codeword (see Fig. 8, "Double bit-error 100% correctable) can be corrected. Since our EDAC is based on single-error-correction and double-error detection, our design can also detect all the remaining combinations of double-bit-errors (see Fig. 8, "Double-bit error 100% Detectable"). All three-bit-errors that are detectable, i.e., when two errors occur on two odd-bits and one on an even-bit of a codeword, and vice versa, are detected by our EDAC. Our EDAC can also detect up to four-adjacent-bit errors. For other detection rate capabilities, see Fig. 1

| Types of Errors   | Codeword         |                  | Description      |

|-------------------|------------------|------------------|------------------|

|                   | Even Bits        | Odd Bits         |                  |

| Single-bit Error  | One Error Bits   |                  | 100% Correctable |

|                   |                  | One Error Bits   |                  |

| Double-bit Errors | One Error Bits   | One Error Bits   |                  |

|                   | Two Error Bits   |                  | 100% Detectable  |

|                   |                  | Two Error Bits   |                  |

| Three-bit Errors  | Two Error Bits   | One Error Bits   |                  |

|                   | One Error Bits   | Two Error Bits   |                  |

|                   | Three Error Bits |                  | 100% Detectable  |

|                   |                  | Three Error Bits |                  |

| Four-bit Errors   | Two Error Bits   | Two Error Bits   | 100% Detectable  |

|                   | One Error Bits   | Three Error Bit  | 100% Detectable  |

|                   | Three Error Bits | One Error Bits   |                  |

|                   | Four Error Bits  |                  |                  |

|                                                                |  | Four Error Bits |  |  |

|----------------------------------------------------------------|--|-----------------|--|--|

| Table. 1: The correctable and detectable errors of EDAC design |  |                 |  |  |

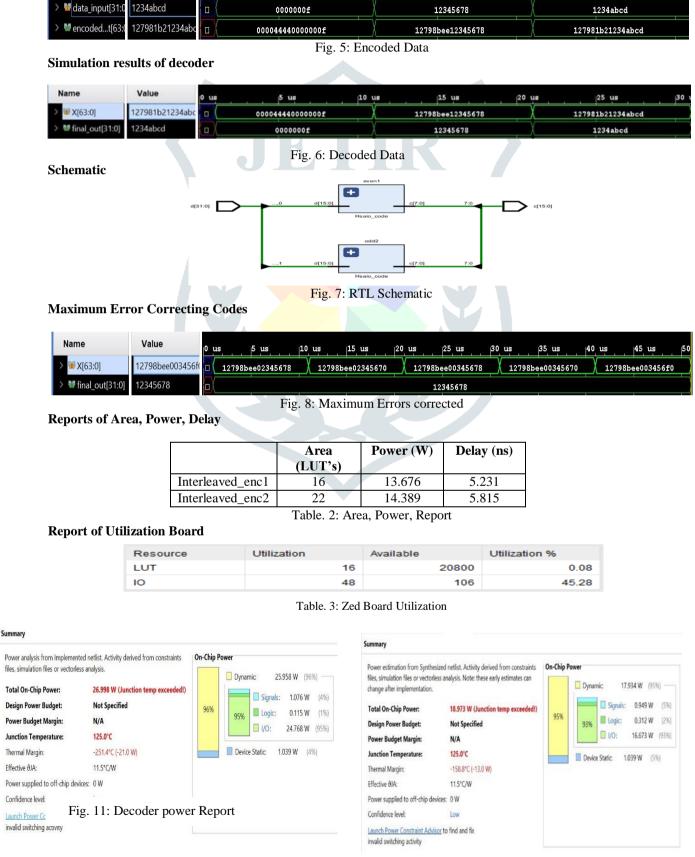

# VI. RESULTS AND DISCUSSION

Simulation Results of Encoder

Fig. 9: Power Report of Encoder

Fig.10: Power Report of Decoder

### VII. CONCLUSION

In this project, two interleaved Double-Adjacent-Error-Correction (DAEC) EDACs can correct single-bit-errors, double adjacent-bit-errors, and double-bit-errors that one error occurs on an even-bit and the other on an odd-bit of a codeword. For error detection, our EDACs can detect up to four-adjacent-bit errors. The detection rates of three-bit-errors are also improved compared to the individual (24,16) EDACs. Both the Hsiao Code and CRC-based EDAC approaches show promising results with minimum hardware requirements. The Hsiao code and CRC for both EDAC can correct 100% of the single-bit-error, double-Adjacent-bit-errors and up to four bits can detect and correct. The Hsiao Code EDAC encoder design requires Less bit weight than the CRC EDAC, which is an attribute of a high-speed EDAC Since the maximum bit-weight per row is low (six for Hsiao Code and seven for CRC), our EDACs are suitable in a high-performance computing system. Since commercial memory devices come in this format, our codeword-storage designs work well with such devices

### VIII. REFERENCES

- 1. M. Y. Hsiao, "A Class of Optimal Minimum Odd-weight-column SECDED Codes," in IBM Journal of Research and Development, vol. 14, no. 4, pp. 395-401, July 1970), DOI: 10.1147/rd.144.0395.

- 2. R. W. Hamming, "Error detecting and error correcting codes," in The Bell System Technical Journal, vol. 29, no. 2, pp. 147-160, April 1950. DOI: 10.1002/j.1538-7305.1950.tb00463.x.

- Reddy, S.M., "A Class of Linear Codes for Error Control in Byte-per Package Organized Memory Systems", IEEE Trans. On Computers, Vol. C-27, pp. 455-458, May. 1978.

- 4. Chen, C. L., "Error Correcting Codes with Byte Error Detection Capability", IEEE Trans. On Computers, Vol. 32, pp. 615-621, May 1983.

- 5. Lin, S., and D. J. Costello, Jr., Error Control Coding: Fundamentals and Applications, Prentice-Hall, 1983.

- 6. Berlekamp, E. R., Algebraic Coding Theory, McGraw-Hill, New York, 1968.

- 7. Lala, P. K., "An Adaptive Double Error Correction Scheme for Semiconductor Memory Systems," Digital Processes, Vol.4, pp 237-243, 1978.

- 8. Hiller, Caleb, Balyan, Vipin, and Zhang, Yagang, "Error Detection and Correction On-Board Nanosatellites Using Hamming Codes," Hindawi, Journal of Electrical and Computer Engineering, Volume 2019, Article ID 3905094, 15 pages. https://doi.org/10.1155/2019/3905094.

- 9. S. Babaie, A. K. Zadeh, S. H. Es-hagi and N. J. Navimipour, "Double Bits Error Correction Using CRC Method," 2009 Fifth International Conference on Semantics, Knowledge and Grid, Zhuhai, 2009, pp. 254-257. DOI: 10.1109/SKG.2009.77.

- 10. P. P. Shirvani, N. R. Saxena and E. J. McCluskey, "Softwareimplemented EDAC protection against SEUs," in IEEE Transactions on Reliability, vol. 49, no. 3, pp. 273-284, Sept 2000. DOI: 10.1109/24.914544.

- 11. Babitha Antony, Divya S, "Modified Hamming Codes with Double Adjacent Error Correction along with Enhanced Adjacent Error Detection," International Journal of Innovative Research in Computer and Communication Engineering, IJIRCCE, August 2015, DOI: 10.15680/IJIRCCE.2015. 0308056.

- 12. Ho-yoon Jun and Yong-surl Lee, "Single error correction, double error detection and double adjacent error correction with no mis-correction code," IEICE Electronics Express, Vol.10, No.20, 1- 2013, DOI: 10.1587/elex.10.20130743